## CS6362 Software Architecture and Design page 1/8

## The University of Texas at Dallas Computer Science Program

|           |     | COIL         | ipatei | Scien | cc 1 10g1 | am      |        |         |        |

|-----------|-----|--------------|--------|-------|-----------|---------|--------|---------|--------|

| Midterm T | est |              |        |       |           |         |        | March 6 | , 1997 |

|           |     | Conditions:  | Closed | book  | Duration  | : 70 m  | inutes |         |        |

|           |     |              |        |       |           |         |        |         |        |

|           |     |              |        |       |           |         |        |         |        |

|           | Na  | me:          |        |       |           |         |        |         |        |

|           |     |              |        | {Plea | se under  | line la | st nam | ie}     |        |

|           | Stu | ident Numbei | . •    |       |           |         |        |         |        |

|           |     | 1            | ·      |       | /20       |         |        |         |        |

|           |     | 2            | •      |       | /20       | -       |        |         |        |

|           |     | 3            | •      |       | /20       |         |        |         |        |

|           |     | 4            | •      |       | /20       |         |        |         |        |

Total\_\_\_\_

/20

| 1. [20 marks] page                                                                                                                                                                                                | 2/8          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| For each of the following ten statements, indicate whether it is true (mark $T$ ) or false (m (No penalty for a wrong answer)                                                                                     | ark F).      |

| This is the mid-term test for CS6362.                                                                                                                                                                             |              |

| $\underline{F}$ 1. All compilers run in a batch mode as this mode is good for conceptual simplicity adaptability.                                                                                                 | ty and       |

| T 2. The correctness of a filter is independent of the correctness of its predecessor filter.                                                                                                                     | lters.       |

| <u>T</u> 3. A software architecture serves as an (abstract) skeleton which can be used to the ability of a system to meet its gross system requirements.                                                          | expose       |

| F 4. Programming-in-the-small focuses on building evolvable software systems, while proceed in-the-large focuses on building efficient data structures and algorithms.                                            | orogramming- |

| <u>F</u> 5. Classical module interconnection languages (MILs) are powerful enough to des variety of architectural styles, such as pipe-and-filter and inplicit invocation.                                        | cribe a      |

| <u>F</u> 6. The single primary role of non-functional requirements during software archit design should be in selecting among software architectural alternatives after the been produced by software architects. |              |

| F 7. In the style of implicit invocation, modules communicate indirectly with each of directly accessing shared data.                                                                                             | ther by      |

| F 8. In a batch sequential architecture, data flows through a sequence of discrete prosteps where update modules can run concurrently with each other.                                                            | cessing      |

| <u>T</u> 9. An essential part of any software architectural design should be design rationale design rationale explains why the particular architecture is chosen from the (p infinitely) large design space.     |              |

| <u>T</u> 10. A semi-formal approach to designing a software architecture is often consider concerning defects but good concerning understandability.                                                              | ed bad       |

2. [20 marks] page 3/8

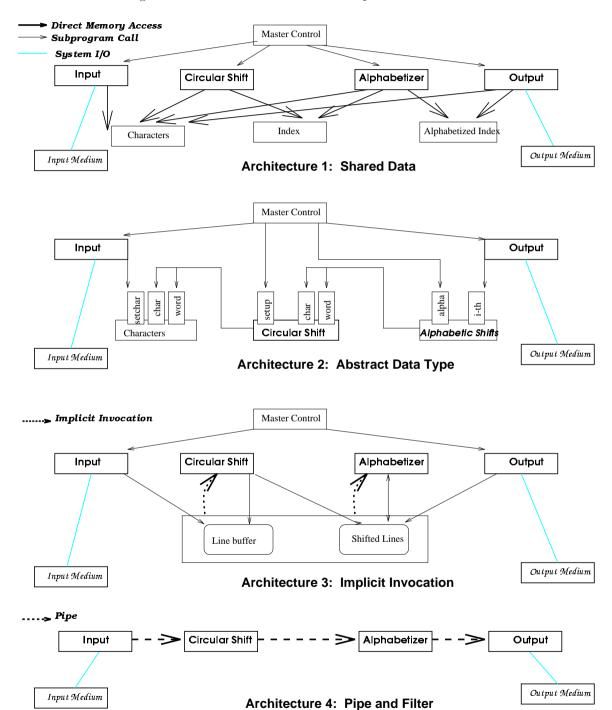

Consider the following four architectures for the KWIC problem.

2. [continued] page 4/8

Consider Architecture 1. Describe briefly what and where modification is needed to efficiently "omit" indices starting with a noise word (e.g., the, a, an, to, and, or, etc.).

After the circular shift; a new "Index-without-noise" will be created and accessed by the Alphabetizer.

- Consider Architecture 1 and Architecture 2. Compare them with respect to reusability and space performance.

- + reuse is better supported in Architecture 2 than in Architecture 1, as modules make fewer assumptions about the others with which they interact

- space performance can be poorer in Architecture 2 than in Architecture 1, if not incremental

- Consider Architecture 3. Suppose the Output module is to be implicitly invoked, instead of being explicitly invoked by the Master Control module. What kind of data should be generated, and by which module and when?

- The Alphabetizer should generate, when it is done with sorting all the circularly shifted lines, "end-of-alphabetization" data.

- Consider Architecture 1 and Architecture 4. Describe briefly the major disadvantage(s) of Architecture 4 when run in a batch mode, when compared to Architecture 1.

- inefficient use of space, as each filter must copy all of the data to its output ports (e.g., all circular shifts in full).

3. [20 marks] page 5/8

Consider the following module declaration:

```

module M

provides: a, b, c, d, e;

requires: v, w, x, y, z;

consist-of: module M1, module M2, module M3

module M1

provides: a;

requires: v;

string a, real v

end M1

module M2

provides: b, c, d;

requires: w, x, y;

has-access-to: module M1

consist-of: module M21, module M22, module M23

module M21

provides: b;

requires: w;

boolean b, integer w

end M21

module M22

provides: c;

requires: x;

has-access-to: module M21

integer c, real x

end M22

module M23

provides: d;

requires: y;

has-access-to: module M22

boolean d, string y

end M23

end M2

module M3

provides: e;

requires: z;

has-access-to: module M2

integer e, z

end M3

end M

```

3. [continued] page 6/8

- 1. List the set of (both internal and external) variables that module M1 has access to.  $\mathbf{a}, \mathbf{v}$

- 2. List the set of (both internal and external) variables that module M21 has access to.  $\mathbf{b}, \mathbf{w}$

- List the set of (both internal and external) variables that module M22 has access to.

c, x, b, w

- 4. List the set of (both internal and external) variables that module M23 has access to.  $\mathbf{d},\,\mathbf{y},\,\mathbf{c},\,\mathbf{x}$

- List the set of (both internal and external) variables that module M3 has access to.

e, z, b, c, d, w, x, y

4. [20 marks] page 7/8

Consider the following declaration of stack:

```

Stack (E, C): trait /* E(e.g., integer, string) is an element of C, a stack */

introduces

new: -> C

push: C, E \rightarrow C

top: C -> E

exempting top(new)

pop: C -> C

exempting pop(new)

isEmpty: C -> Bool

asserts

C generated by new, push

forall stk: C, e: E

top (push(stk, e)) == e

pop (push(stk, e)) == stk

isEmpty(new)

" isEmpty(push(stk, e))

implies

LinearContainer (push for insert, top for first, pop for rest)

```

1. What is the value of pop (top (stk)) for any stk: C?

## undefined

2. What is the value of top (push (new, e)) for any e: E?

$\mathbf{e}$

- 3. What is the value of pop (push (new, e)) for any e: E?

the stack generated by "new

- 4. What is the value of is Empty (pop (push (new, e))) for any e: E? true

- 5. What is the value of pop (push (push (new, e), e'))) for any e, e': E?

the stack generated by "new" containing e

- 6. What is the value of is Empty (pop (push (push (new, e), e'))) for any e, e': E? true

- 7. What is the value of top (pop (push (push (new, e), e'))) for any e, e': E?

e

- 8. What is the value of top (pop (pop (push (push (new, e), e')))) for any e, e': E? undefined

- 9. What is the value of rest (rest (insert (new, e))) for any e: E, assuming that LinearContainer has access to Stack?

## undefined

10. What is the value of first (insert (rest (insert (new, e)), e')) for any e, e': E, assuming that LinearContainer has access to Stack?

e'

5. [20 marks] page 8/8

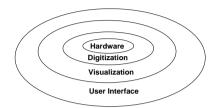

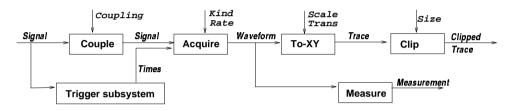

Consider the following two architectures for an oscilloscope, as discussed in class:

**Architecture 1**

Architecture 2

- 1. [8 marks] Describe in relation to Architecture 2 one major problem with Architecture 1.

- boundaries of abstraction conflicted with the needs for function interactions e.g., requires all user interactions with an oscilloscope thru the visual representations

but, users need to affect the functions in all layers:

- e.g., setting channels in Hardware layer; choosing acquisition mode & parameters (e.g., threshold value) in Digitization layer; creating derived waveforms (e.g., scaling factor) in Visualization layer.

- 2. [8 marks] What kind of mechanism would be needed to display Measurement on the screen?

A mechanism to:

- convert raw measurements to scaled, translated, and clipped measurements (font size, etc. need to be determined as well)

- **3.** [4 marks] Pictorially depict a 2-layer architecture which can be obtained from *Architecture* 2.