# Device Modeling and Circuit Design for Scalable Beyond-CMOS Computing

Xuan Hu<sup>1</sup>, Naimul Hassan<sup>1</sup>, Wesley H. Brigner<sup>1</sup>, Maverick Chauwin<sup>1,2</sup> and Joseph S. Friedman<sup>1</sup>

<sup>1</sup>Electrical & Computer Engineering, The University of Texas at Dallas, Richardson, TX, United States <sup>2</sup>Department of Physics, École Polytechnique, France

Abstract—Emerging technologies provide potential solutions to overcome the limitations of modern CMOS technologies. Specifically, as power density limitations impede further CMOS scaling, emerging technologies including spintronics, memristors, ambipolar transistors, and other beyond-CMOS devices are promising replacements for conventional CMOS transistors due to features such as non-volatility, low energy consumption, high operation speed, or high logical expressiveness. Specifically, we have evaluated spintronic technologies such as domain wall-magnetic tunnel junctions (DW-MTJs) and magnetic skyrmions that are particularly exciting for highly-efficient non-volatile information processing. Additionally, we have explored unconventional electronic switching devices including ambipolar transistors and memristors as replacements to CMOS and for hybrid emerging technology-CMOS computing systems.

Keywords—emerging technology, spintronics, compact modeling, ambipolarity, neuromorphic computing

#### I. INTRODUCTION

Beyond-CMOS computing is being explored with novel devices, architectures, and computing paradigms. For the development of these emerging technologies, it is critical to be able to directly-cascade devices without extra circuitry in scalable computing systems without CMOS. These beyond-CMOS devices and circuits exhibit the versatility and scalability of emerging technologies.

# II. SPICE-COMPATIBLE MODELING OF BEYOND-CMOS COMPUTING DEVICES

As the fabrication processes for emerging technologies are relatively immature, it is important to develop device models that are able to accurately and efficiently simulate medium-to-large scale circuits. These simulation results can be used to compare the efficiency of these emerging technologies and provide feedback for system prototype fabrication.

## A. Modeling & Circuit Design of Ambipolar Carbon Nanotube Field-Effect Transistors

Ambipolar semiconductor transport provides exciting opportunities for computing and has been experimentally demonstrated in various materials including carbon nanotubes (CNTs), silicon nanowires (SiNWs), and transition metal dichalcogenide (TMD) monolayers, enabling ambipolar transistors in which the majority carrier type can be switched dynamically. This flexibility enables compact circuit design by integrating more functionalities into fewer devices, but leads to fundamentally new challenges for device modeling.

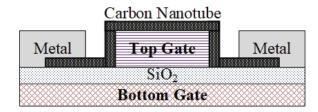

Fig. 1. Cross-section diagram of dual-gate ambipolar field-effect transistor (adapted from [1]).

Fig. 1 demonstrates the cross-section diagram of a dual-gate ambipolar carbon nanotube field-effect transistor (DG-A-CNTFET), in which both the top and bottom gates can be used to modulate the current through the CNT [1]. In addition, the bottom gate can be used to switch the transistor polarity, permitting the CNTFET to operate as an ambipolar device. We have therefore developed a closed-form SPICE-compatible model [2], [3] for dual-gate ambipolar transistors with the ability to dynamically switch the transistor polarity and interchange the terminals. This has enabled the first transient simulations of ambipolar CNTFET-based logic circuits in which the transistor polarity switches during the simulation, permitting the development of large-scale computing systems that fully exploit ambipolar transport.

## B. SPICE-Only Model for Spin-Transfer Torque Domain Wall MTJ Logic

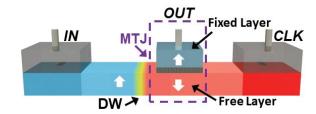

The spin-transfer torque domain wall (DW) magnetic tunnel junction (MTJ) enables spintronic logic circuits that can be directly cascaded without deleterious signal conversion circuitry and is one of the only spintronic devices for which cascading has been demonstrated experimentally [4], [5]. Fig. 2 shows the diagram of the DW-MTJ device: the current flow through the bottom soft ferromagnetic track shifts the position of the DW which leads to the resistance switching of the MTJ formed by

Fig. 2. Device diagram of DW-MTJ.

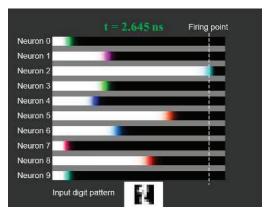

Fig. 3. Simulation snapshot of the output neuron layer for a hand-written digit recognition task composed of ten DW-MTJ neurons.

the combination of the soft ferromagnetic layer, the fixed layer, and the tunnel barrier.

To accelerate the design and simulation of large-scale DW-MTJ systems, we proposed a SPICE-only compact model [6] that is directly compatible with modern circuit design CAD tools. Compared to the previous simulation techniques, the proposed model enables accurate and rapid simulation with 10,000x decrease in simulation speed.

# III. NEUROMORPHIC AND BOOLEAN CIRCUIT DESIGN WITH SPINTRONIC DEVICES

The increasing leakage and instability of scaled CMOS memories inhibit their application in further neuromorphic or other non-von Neumann computing systems, whereas spintronic devices have been proven to be suitable and efficient for neuromorphic computing and versatile logical systems. It is therefore important to develop spintronic computation and signal processing circuits in addition to CMOS, as conventional transistors do not effectively emulate neurobiological behavior.

## A. Artificial Neuron with DW-MTJ

In light of the non-volatility, low-energy consumption, scalability, and its natural analog to biological neuron behavior, the DW-MTJ in Fig. 2 is used to implement a leaky integrate-and-fire (LIF) artificial neuron [7]. Fig. 3 shows a snapshot of the hand-written digit recognition simulation using the proposed LIF neuron, in which the system correctly identifies 94% of the digits in the task simulated. This system, in concert with artificial synapses with the same device [8], enable purely-spintronic neuromorphic computing systems without CMOS.

### B. Scalable Skyrmion Logic System

Magnetic skyrmions are topologically-stable magnetic whirls that have been proposed as highly-efficient information carriers for computing systems that exploit the fact that these quasiparticles are small, non-volatile, and can be propagated with minimal energy. Reversible computing, meanwhile, is a computing paradigm that conserves information, leading to theoretical proposals for non-dissipative computing systems based on conservative logic that consume zero energy. By combining the concept of conservative logic with the features of skyrmions, we have proposed a nanoscale conservative

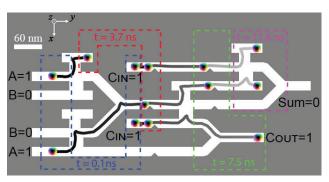

Fig. 4. Micromagnetic simulation of skyrmion-based one-bit full adder.

skyrmion logic system and demonstrated the ability to perform cascaded logical operations [9]. Fig. 4 shows the schematic of a skyrmion-based one-bit full adder. This system includes a synchronization circuit that enables the realization of large-scale non-volatile spintronic computing systems with high operating speed and low energy consumption.

#### IV. CONCLUSIONS

By exploiting low-energy switching, reconfigurability, non-volatility, and unique operating mechanisms, these emerging technologies provide the potential to revolutionize information processing for the next generation of computing systems. However, the development and application of these novel devices in large-scale systems are impeded by the lack of proper simulation techniques and inefficient circuit topologies. Here we described the models for different emerging technology devices which enable rapid and accurate simulations in different scales of systems. We also discussed the characteristics and efficient applications of novel spintronic devices in various paradigms for next-generation computing systems.

#### REFERENCES

- Y. Lin, J. Appenzeller, and P. Avouris, "Novel carbon nanotube FET design with tunable polarity", *IEDM*, pp. 687-690, 2004.

- [2] X. Hu and J. S. Friedman, "Closed-Form Model for Dual-Gate Ambipolar CNTFET Circuit Design", *IEEE ISCAS*, May 2017.

- [3] X. Hu and J. S. Friedman, "Transient Model with Interchangeability for Dual-Gate Ambipolar CNTFET Logic Design", IEEE/ACM Nanoarch, July 2017.

- [4] J. A. Currivan, Y. Jang, M. D. Mascaro, M. A. Baldo, and C. A. Ross, "Low energy magnetic domain wall logic in short, narrow, ferromagnetic wires," *IEEE Magn. Lett.*, vol. 3, 2012, Art. no. 3000104.

- [5] J. A. Currivan-Incorvia et al., "Logic circuit prototypes for threeterminal magnetic tunnel junctions with mobile domain walls," *Nature Commun.*, vol. 7, Jan. 2016, Art. no. 10275.

- [6] X. Hu, A. Timm, W. H. Brigner, J. A. C. Incorvia, and J. S. Friedman, "SPICE-only model for spin-transfer torque domain wall MTJ logic," *IEEE Trans. Electron Devices*, vol. 66, no. 6, pp. 2817–2821, Jun. 2019.

- [7] N. Hassan et al., "Magnetic domain wall neuron with lateral inhibition," J. Appl. Phys., vol. 124, no. 15, 2018, Art. no. 152127.

- [8] O. Akinola, X. Hu, C. H. Bennett, M. Marinella, J. S. Friedman, and J. A. C. Incorvia, "Three-Terminal Magnetic Tunnel Junction Synapse Circuits Showing Spike-Timing-Dependent Plasticity", *Journal of Physics D: Applied Physics*, vol. 52, no. 49, 2019, Art. no. 49LT01.

- [9] M. Chauwin\*, X. Hu\*, F. Garcia-Sanchez, N. Betrabet, A. Paler, C. Moutafis, and J. S. Friedman, "Skyrmion Logic System for Large-Scale Reversible Computation", *Physical Review Applied*, vol. 12, no. 6, p. 064053 (2019).