Joseph S. Friedman

| Joseph S. Friedman |

|

|

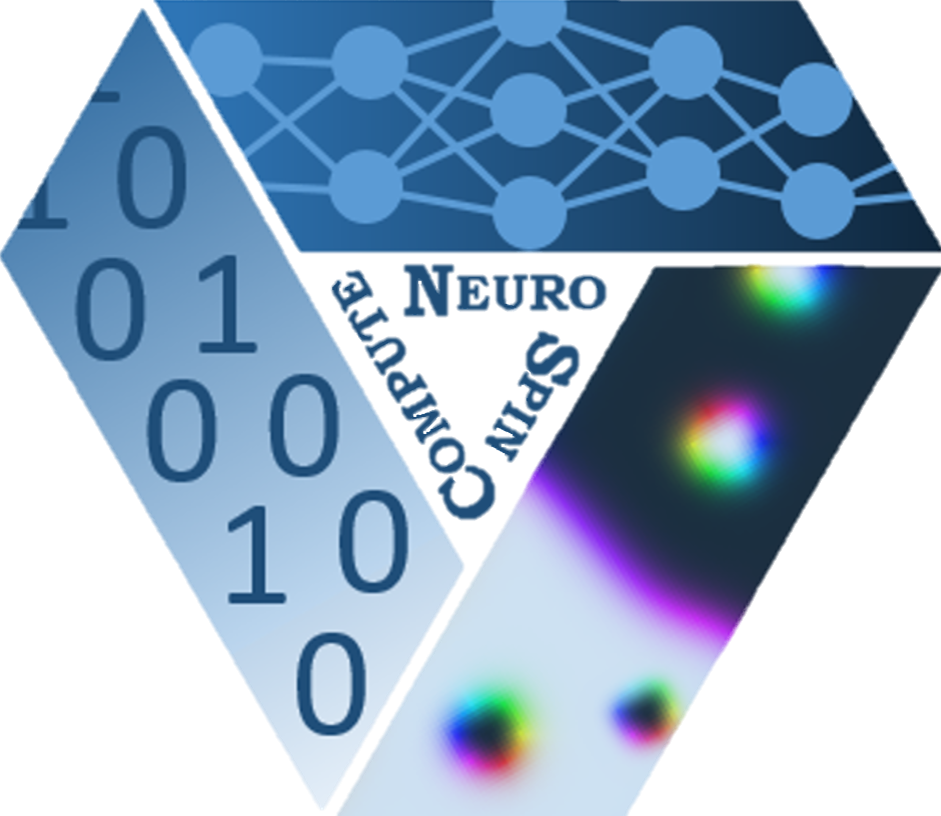

All-Carbon Spin LogicIn all-carbon spin logic (ACSL), magnetoresistive graphene nanoribbons (GNRs) are connected by carbon nanotubes (CNTs) in logical circuits with extreme speed and energy-efficiency. The exceptional properties of low-dimensional carbon, in concert with electromagnetic wave-based signal propagation, provide the potential for terahertz operation and a 100x improvement in power-delay product.All-Carbon Spin Logic GateThe basis logic gate in ACSL is composed of a magnetoresistive GNR with a parallel CNT control wire adjacent to each GNR edge. Currents through the CNTs create magnetic fields along the GNR edges that control the global magnetic ordering, thereby modulating the GNR conductivity. A constant voltage is applied to the GNR, and the relative directions and magnitudes of the CNT input currents (IA and IB) can be used to switch the GNR output current (IO).Binary logic states are defined in ACSL as large "1" and small "0" currents. Large CNT input currents are sufficient to switch the GNR edge magnetization between resistive antiferromagnetic (AFM) global ordering and conductive ferromagnetic (FM) global ordering. The two control wire inputs produce the logical OR function when the CNT currents are in opposite directions, and the XOR function when the CNT currents are in the same direction.

Cascaded All-Carbon Spin Logic CircuitsACSL circuits can be realized by using the GNR output currents IO as CNT control wire inputs to other ACSL logic gates. To enable cascading, GNRs are covalently bonded to CNT control wires that drive other GNR logic gates. Each GNR is connected by CNTs directly to V+ and V- nodes, with these CNTs routed adjacent to other GNRs to propagate information to cascaded GNR logic gates. Additionally, wired-OR gates can be used to perform the logical OR function without requiring a GNR device. As shown below, four GNR XOR gates and three wired-OR gates can be integrated to realize a one-bit full adder.

Performance & Energy EfficiencyThe delay and power dissipation mechanisms in ACSL are quite different from conventional CMOS. As the state variable is current rather than voltage, there is no need for gates to accumulate charge with an RC delay. Instead, the combined ACSL interconnect and gate delays result from:

Related Publications

*from Nature Communications 8, 15635 under CC BY 4.0* |