|

|

|

|

Stateful Memristor Logic

The non-volatility of memristors enables stateful logic, in which bits are encoded as binary resistance states.

However, an alaysis of the required control circuit shows that when this overhead circuitry is included, stateful memristor logic is one billion times less efficient than conventional CMOS logic!

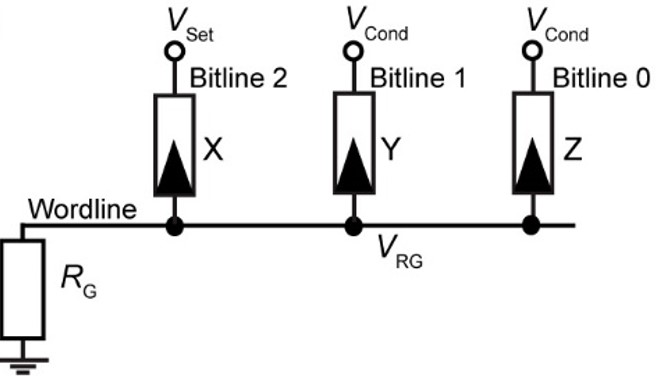

Memristor Logic Operation

Current flow through a memristor in one direction causes the memristor to switch to a low-resistance state, while current flow in the other direction increases the resistance.

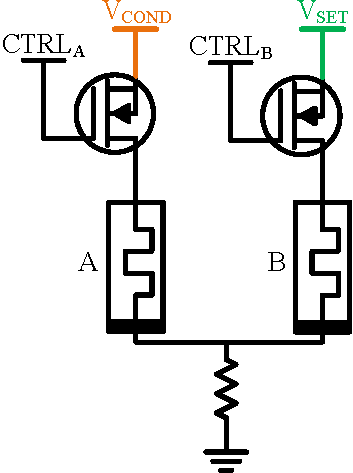

In stateful memristor logic, voltages are applied to two memristors such that one memristor (B, in the figure) switches dependent on the states of the two memristors.

This performs the "implication" function A -> B, more simply written as A \/ B.

Overhead Circuit & Inefficiency

Though much previous research has claimed that stateful memristor logic provides enormous advantages over CMOS, such claims have ignored the hardware cost of the control circuit required to drive the memristor logic operations.

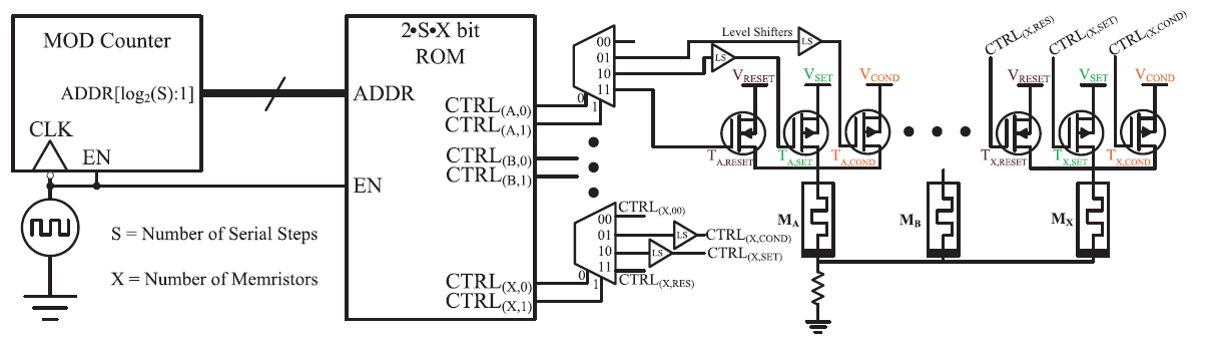

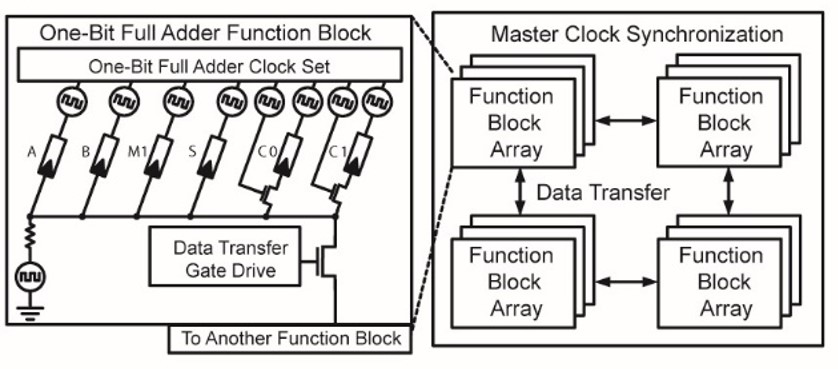

As depicted in the figure below, the required overhead control circuit is quite complex.

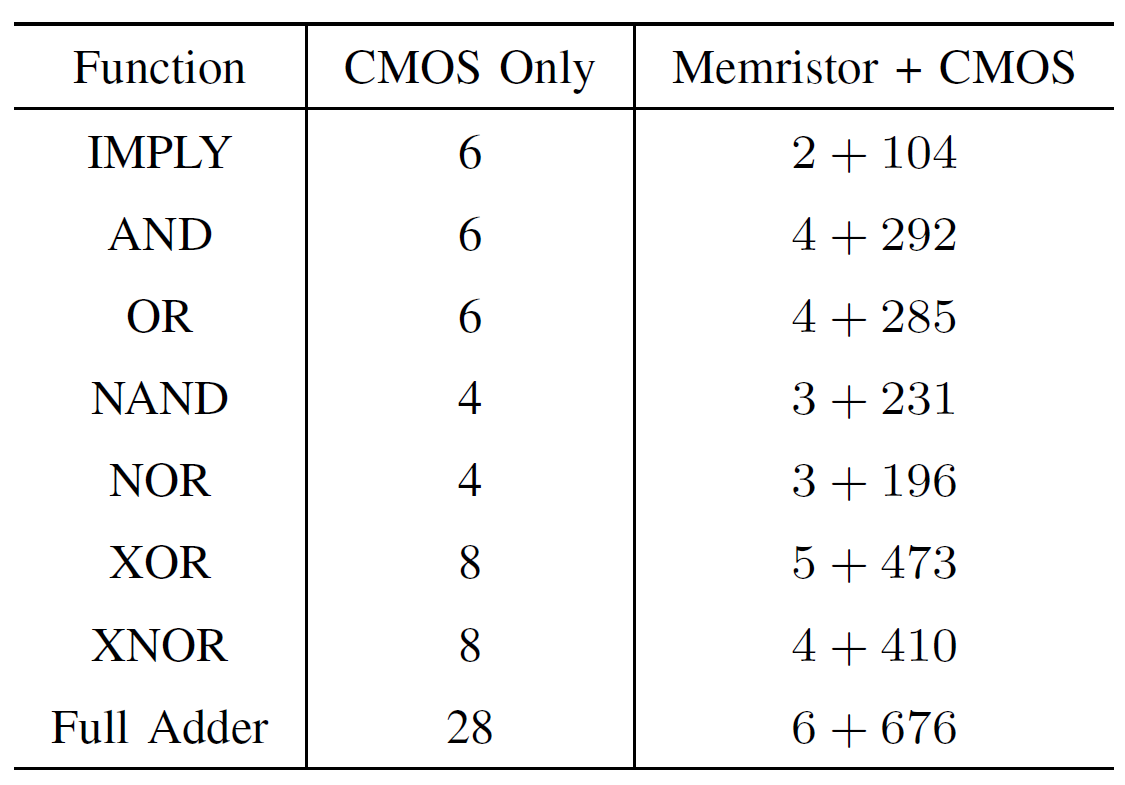

In fact, the CMOS control circuit for a memristor logic operation requires more CMOS transistors than a conventional CMOS logic circuit that performs the same operation!

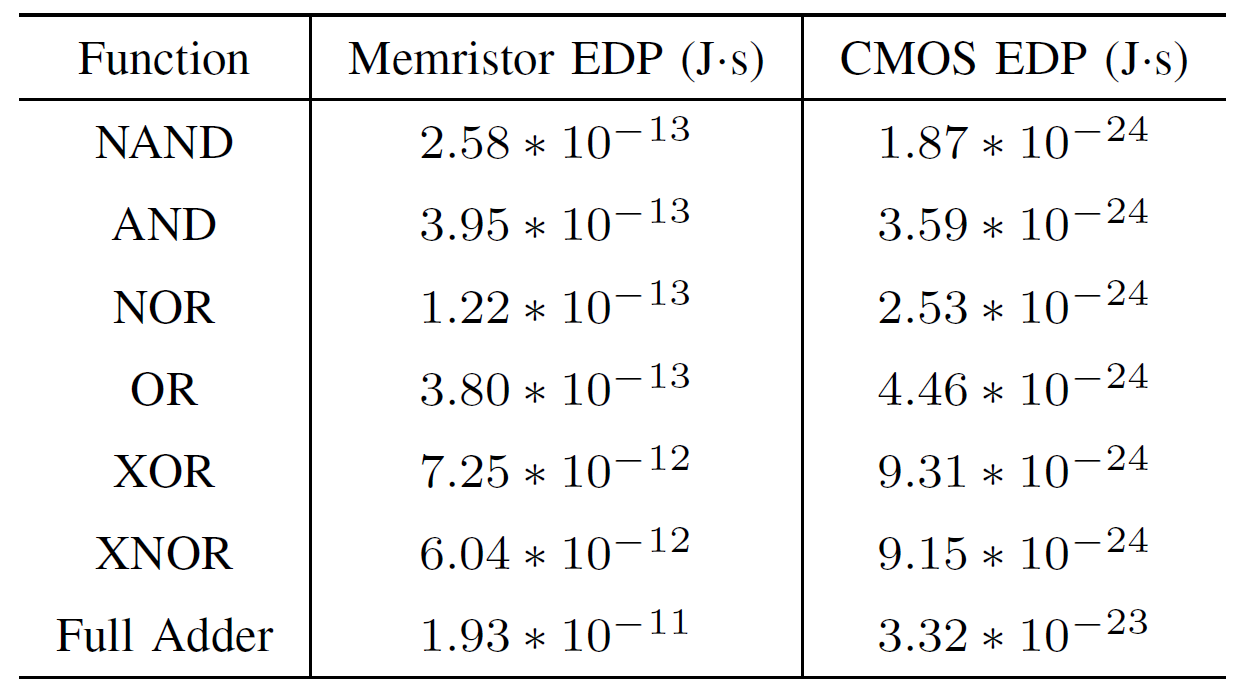

This results in stateful memristor logic exhibiting an efficiency (as measured by energy-delay product and power-delay product) that is one billion times worse than conventional CMOS!

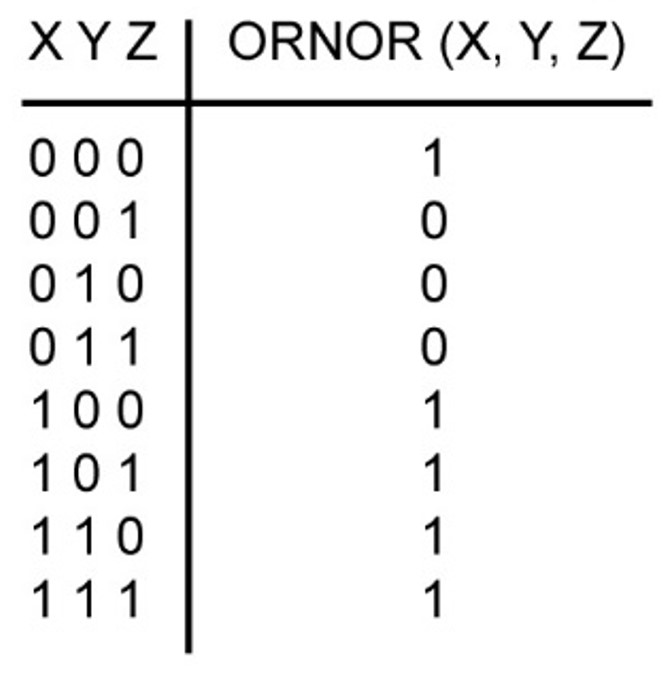

Three-Input Memristor Logic

To improve the efficiency of stateful memristor logic, it is critical to decrease the number of steps required to perform logic functions.

The use of three-input stateful memrsitor logic enables a significantly more complex logical function to be performed within each step, thereby reducing the total number of steps required.

Furthermore, the complexity of the overhead control circuit can be drastically reduced by simultaneously providing control signals to multiple rows of memristors in parallel.

By organizing memristor arrays into large function blocks, the required control circuitry can be leveraged by numerous memristor rows in parallel with a global clocking sequence, thereby distributing the hardware overhead accross the entire array.

Related Publications

- X. Hu, M. J. Schultis, M. Kramer, A. Bagla, A. Shetty, J. S. Friedman, Control Circuit Overhead for Stateful Memristor Logic, IEEE International Conference on Rebooting Computing, Dec. 2020.

- X. Hu, M. J. Schultis, M. Kramer, A. Bagla, A. Shetty, J. S. Friedman, Control Circuit Overhead for Stateful Memristor Logic, IBM/IEEE AI Compute Symposium, Oct. 2020.

- A. Siemon, R. Drabinski, M. J. Schultis, X. Hu, E. Linn, A. Heittmann, R. Waser, D. Querlioz, S. Menzel, J. S. Friedman, Stateful Three-Input Logic with Memristive Switches, Scientific Reports 9, 14618 (2019).

- X. Hu*, M. J. Schultis*, M. Kramer, A. Bagla, A. Shetty, J. S. Friedman, Overhead Requirements for Stateful Memristor Logic, IEEE Transactions on Circuits & Systems I 66:1, 263-273 (2019).

- X. Hu*, M. J. Schultis*, M. Kramer, A. Bagla, A. Shetty, J. S. Friedman, Overhead Requirements for Stateful Memristor Logic, IEEE International Symposium on Circuits & Systems, May 2019.

|