Design Automation and Reconfigurable Computing Laboratory (DARClab)

Welcome to UTD's DARClab. As the name indicates we mainly work on VLSI Design Automation and Reconfigurable Computing (FPGAs) topics

The aim of this group is to do significant research in the areas of VLSI Design Automation and Reconfigurable Computing. Our goal is finding important problems, formulating the problems systematically, and solving them effectively. The target of our optimizations covers both hardware and software. This includes but is not limited to Electronic Design Automation (EDA) problems such as hardware synthesis problems (from system down to circuit level) and embedded software (compiler, operating system) optimization problems. One of the key aspects of our lab is that we only use high-level languages to build hardware circuits. The ultimate goal of the lab is to fully move away from low-level hardware description langauges like Verilog or VHDL and only use C/C++, SystemC, Python or Matlab.

We do put a big emphasis on the demonstation of the solutions and aim at releasing the software and hardware implementation to the community. For this we relay heavily on FPGAs, thus, the name of our lab.

Another research direction that we are actively persuing covers the area of Design for Trust (DFT).

DARClab News

Follow us on twitter to keep updated about our latest work

High-Level Synthesis Made Easy - April 2024

We have just published a HLS book called HLS made easy. The pdf version of the book is free and a printed hard copy can be ordered through Amazon here.

highX Technologies - Feburary 2023

Today we annouce the creation of highX Technologies, a spin-off the DARClab that builds upon the technology and expertise accumulated during the last 12 years at the lab. highX Technologies is dedicated to making hardware design easier by providing Behavioral IPs written in ANSI C and SystemC optimized for High-Level Synthesis (HLS). The company also provides HLS and FPGA consulting and training courses. More information at highX services.

ConTex scholarships for Mexican Students- Becas para estudiantes Mexicanos- January 2021

Mexican students intersted in pursuing PhD studies in the area of reconfigurable computing, computer architecture and EDA at the DARClab are invited to apply

through the ConTex program [ConTex info español]

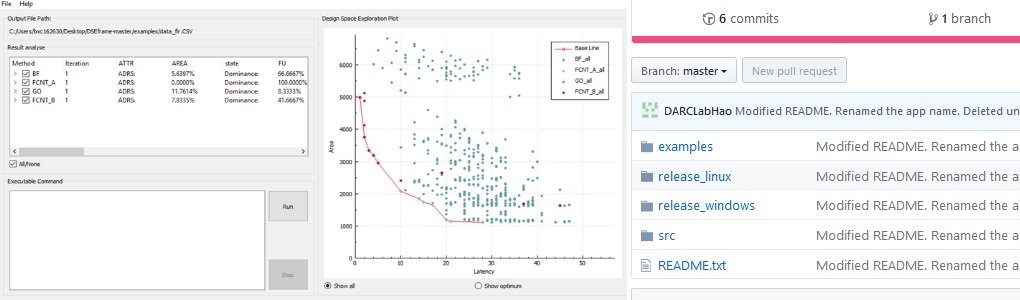

HLS Design Space Exploration Framework (DSEFrame) v1.0 released - Feburary 2019

Version 1.0 of a GUI-based High-Level Synthesis DSE framework was just released. DSEframe v1.0 can be downloaded from [Github]

S2Cbench version 2.2 released- Feburary 2018

Version 2.2 of the popular SystemC benchmark suite has been released. The benchmarks can be downloaded from [Resources]

DARClab Videos

For more videos visit our Youtube channel (DARClabify)