# Concurrent Detection of Erroneous Responses in Linear Analog Circuits

Haralampos-G. D. Stratigopoulos, Student Member, IEEE, and Yiorgos Makris, Member IEEE

Abstract—This paper presents a novel methodology for concurrent error detection in linear analog circuits. The error-detection circuit monitors the input and some observable internal nodes of the examined circuit and generates an estimate of its output. The estimate coincides with the output in error-free operation, while in the presence of errors, it diverges. Thus, concurrent error detection is performed by comparing the two signals through an analog comparator. In essence, the error-detection circuit operates as a duplicate of the examined circuit, yet it is smaller, in general, and never exceeds the size of an actual duplicate. The proposed methodology is demonstrated on three analog filters.

Index Terms—Analog test, concurrent error detection, linear analog circuits, state observation.

#### I. Introduction

NALOG test solutions are essential to the success of mod-A ern systems that comprise analog interfaces [1]. While off-line test methods are capable of detecting manufacturing faults, wear-and-tear faults and transient errors require additional care. In high-safety applications, a circuit should monitor itself and report potential deviations from its correct functionality through a concurrent-error-detection mechanism. Concurrent error detection is achieved by continuously examining whether an inherent or imposed invariant property of the circuit is satisfied. This property should reflect valuable information regarding the operational health of the circuit and, ideally, should deviate from its nominal state if and only if an error occurs in the response of the circuit. The objective of concurrent error detection in analog circuits is to examine whether the invariant signal remains within a predefined band around its nominal value and to indicate any deviation that is unacceptably large.

The invariant is realized and concurrently checked by additional on-chip circuitry. The main challenges in designing such circuitry are related to the retrieval and processing of information to generate the invariant. In particular, retrieving and processing are steps that should be performed continuously and in parallel with the normal operation of the monitored circuit, without interrupting or degrading its performance. Continuous processing implies that the error-detection circuit must respond

Manuscript received March 31, 2004; revised December 6, 2004 and March 29, 2005. This paper was recommended by Associate Editor S. M. Reddy.

H.-G. D. Stratigopoulos is with the Department of Electrical Engineering, Yale University, New Haven, CT 06520-8285 USA (e-mail: haralampos-g. stratigopoulos@vale.edu).

Y. Makris is with the Departments of Electrical Engineering and Computer Science, Yale University, New Haven, CT 06520-8285 USA (e-mail: yiorgos. makris@yale.edu).

Digital Object Identifier 10.1109/TCAD.2005.855962

accurately to all realistic input signals at the speed of operation. The various signals that are combined to construct the invariant should be synchronized in order to avoid inadvertent violation due to phase lags. The error-detection circuit should also translate the invariant into a test criterion that can be evaluated concurrently. In order to optimize error detection, this test criterion should reflect the compliance of the circuit response to its performance parameters. Otherwise, the probability of false alarms would become nonnegligible. Last but not least, an efficient concurrent-error-detection method should result in an error-detection circuit of smaller size than the monitored circuit. Otherwise, duplication would be a more palatable choice.

In this paper, we present a novel concurrent-error-detection method for linear analog circuits that meets the aforementioned objectives. After discussing related work in Section II, we provide a conceptual overview of the proposed method in Section III. The mathematical foundation and the implementation details of the proposed method are presented in Sections IV–IX. Finally, in Section X, we provide experimental results on three example circuits that validate the theory and demonstrate the practical viability of our method.

#### II. RELATED WORK

A comprehensive overview of previously proposed methodologies for concurrent error detection in analog circuits can be found in [2]. This topic has attracted increased interest recently, particularly for the class of linear circuits.

The simplest way to perform concurrent testing is to duplicate the system and compare the outputs of the two replicas while they are driven by a common input. The authors in [3] propose a strategy that avoids full replication of the system, provided that some modularity exists. In particular, a universal biquadratic section, which is able to mimic any of the filter types, is successively programmed to match the function of every filter stage.

In [4], the time-invariant matrices of the state-variable equations are encoded into a single continuous checksum as coefficients of observable signals and their derivatives. The error signal is then generated by a cascade of voltage-summing configurations and integrators. An extension of this work is presented in [5], where the authors derive an optimal design of the error-detection circuit that minimizes the number of false alarms under specific fault assumptions. The optimization problem consists of finding appropriate values for the elements of the coding vector. Another algorithm, presented in [6], finds the coding vector that realizes the optimal error-detection circuit in terms of hardware overhead.

The idea discussed in [4] is also applicable to linear digital state-variable systems with appropriate modifications [7]. An extension of this work is presented in [8], where the state space is expanded by embedding the original system into a larger redundant one. It is shown how to select the redundant dynamics and the coding matrix that allow tracking of error propagation during the operation of the system and, thus, enable nonconcurrent detection of errors.

In [9], the authors take k successive derivatives of the output state-space expression and combine the k equations in a matrix form. k is chosen such that the coefficient matrix that multiplies the state-variable vector is nonsingular. The combined equation is multiplied by a vector that projects the coefficient matrix to 0. This eliminates the state variables and results in a residual of inputs, outputs, and their derivatives up to the order necessary to generate a nonsingular coefficient matrix. An error-detection circuit computes this residual and generates a fault-indicating signal whenever it deviates from 0.

In [10], the system is represented in its state-space form by eliminating redundant node voltages. Subsequently, state variables are judiciously deleted from the system of state equations, ensuring that all circuit components are represented in the reduced system. The final set of equations is composed into an invariant signal. If k states are deleted and n is the order of the original circuit, then the order of the circuit that monitors the invariant signal is n+k.

## III. METHODOLOGY OVERVIEW

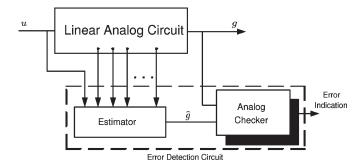

The general framework of the proposed method is depicted in Fig. 1. Given a linear analog circuit, we construct an errordetection circuit that monitors its operation and asserts an output indication whenever an error occurs. The error-detection circuit consists of an estimator and an analog checker. The estimator is a linear dynamic circuit that monitors the inputs and a select set of observable nodes and estimates the output. In error-free operation, the estimate  $\hat{q}$  converges exponentially to the output g with a time constant that can be controlled to be arbitrarily small. Once convergence is accomplished, the difference  $g - \hat{g}$  remains invariably 0. If an error occurs,  $\hat{q}$  diverges from q and, thus, this invariant is violated. The analog checker is used to compare g to  $\hat{g}$  and generate an error indication whenever their difference is unacceptably large. The key points of the proposed methodology and the corresponding sections where they are discussed are outlined below.

- 1) The estimator is designed based on a formal method for estimating nonobservable state variables of a linear dynamic circuit. Therefore, in the error-free case, g and  $\hat{g}$  converge by construction. The corresponding theory and a theorem proving that convergence can be made arbitrarily fast are provided in Section IV. Appropriate realization of the output estimate  $\hat{g}$  is discussed in Section V.

- 2) Divergence in the presence of an error occurs because, despite sharing the observable nodes, the circuits computing the two signals are fundamentally different and, thus, are affected distinctly by the error. In Section VI, we discuss the ability of the estimator to reflect errors

Fig. 1. Signal flow in the proposed concurrent-error-detection method.

affecting any circuit component. Moreover, the estimator and the analog checker indicate their own faults or retain the ability to process the retrieved information correctly. Thus, in Section VII, we conclude that the system is totally self-checking (TSC).

- 3) The order of the estimator equals at most the number of node voltages that need to be estimated. Thus, the estimator is less complex than a duplicate of the circuit, which generally implies that it occupies less area. In essence, the estimator duplicates the response of the monitored circuit, but it is smaller since it shares information available in its observable nodes. Estimator-size issues are discussed in Section VIII.

- 4) In order to provide an error indication whenever the invariant is violated, the output and its estimate are continuously compared through the analog checker. The checker establishes a threshold within which the two analog signals are deemed equal. Checker design issues are discussed in Section IX.

## IV. ESTIMATING NONOBSERVABLE STATE VARIABLES

A linear time-invariant analog circuit has the following statevariable representation:

$$\dot{x} = Ax + Bu$$

$$g = Cx + Du \tag{1}$$

where u is the  $m \times 1$  input vector, x is the  $n \times 1$  state-variable vector, g is the  $\ell \times 1$  output vector and A, B, C, and D are real-valued matrices of appropriate dimensions. Suppose that p state variables are observable, namely, we can monitor their value without affecting the normal operation of the circuit. Let  $x_{\alpha}$  and  $x_{\beta}$  denote the  $p \times 1$  observable and  $(n-p) \times 1$  nonobservable parts of x.  $x_{\alpha}$  and x are linked with a x0 transformation matrix x1 that has rank x2

$$x_{\alpha} = Yx. \tag{2}$$

Let  $P^{-1}$  be

$$P^{-1} = \begin{bmatrix} Y \\ P_{\rm b} \end{bmatrix} \tag{3}$$

where  $P_{\rm b}$  is an  $(n-p) \times n$  matrix that has Boolean elements subject to the requirements that P is indeed invertible. We

rearrange the state-variable vector x by applying the transformation  $P^{-1}$ , such that the first p elements of the new vector x' correspond to the p observable state variables

$$x' = \begin{bmatrix} x_{\alpha} \\ x_{\beta} \end{bmatrix} = P^{-1}x. \tag{4}$$

The first equation in (1) can now be written as

$$\dot{x}' = Fx' + Gu \tag{5}$$

where  $F = P^{-1}AP$  and  $G = P^{-1}B$ . Equation (2) can also be written as

$$x_{\alpha} = YPx'$$

$$= \begin{bmatrix} I_p & 0_{p \times (n-p)} \end{bmatrix} x'. \tag{6}$$

The partitioned form of (5) is

$$\begin{bmatrix} \dot{x}_{\alpha} \\ \dot{x}_{\beta} \end{bmatrix} = \begin{bmatrix} F_{11} & F_{12} \\ F_{21} & F_{22} \end{bmatrix} \begin{bmatrix} x_{\alpha} \\ x_{\beta} \end{bmatrix} + \begin{bmatrix} G_1 \\ G_2 \end{bmatrix} u. \tag{7}$$

In the following, we show how to generate an asymptotic estimate of the n-p state variables  $x_\beta$  through a linear dynamic system that monitors u and  $x_\alpha$  [11]. Our aim is to define a linear observer of the general form

$$\dot{x}_{\gamma} = Hx_{\gamma} + Kx_{\alpha} + \Gamma u$$

$$\hat{w} = x_{\gamma} + Nx_{\alpha}$$

(8)

in such a way that along any trajectory of the combined linear system (5)–(8),  $\hat{w}$  converges to the nonobservable part  $x_\beta$  in the limit  $t\to\infty$

$$\lim_{t \to \infty} (\hat{w} - x_{\beta}) = 0. \tag{9}$$

For this purpose, we define the error difference

$$e_{\beta} = x_{\beta} - \hat{w}. \tag{10}$$

For  $\hat{w}$  to asymptotically estimate  $x_{\beta}$ , it is therefore adequate to ensure that  $e_{\beta}$  converges to 0 as  $t \to \infty$ . Using (7) and (8) and after some simple algebraic manipulations, we obtain the following error differential equation:

$$\dot{e}_{\beta} = He_{\beta} \tag{11}$$

provided that the conditions below are satisfied

$$H = F_{22} - NF_{12}$$

$K = F_{21} - NF_{11} + HN$

$\Gamma = G_2 - NG_1.$  (12)

The solution of (11) can be written as

$$e_{\beta}(t) = \Phi_H(t, 0)e_{\beta}(0) \tag{13}$$

where  $\Phi_H(t,0) = \mathrm{e}^{Ht}$  is the transition matrix of H. Hence, if we choose an exponentially stable t matrix t, then t matrix t, then t matrix t m

Using the Jordan normal form of H, it can be shown that H is exponentially stable if and only if all its eigenvalues have negative real parts [11]. Moreover, the dominant time constant of the exponential decay  $\|\mathbf{e}^{Ht}\| \to 0$  is  $1/\lambda_m$ , where  $\lambda_m$  is the largest eigenvalue of H. The following theorem states that the convergence can be made arbitrarily fast if the time-invariant linear state system (5) and (6) is observable. The proof is outlined in the Appendix.

Theorem 1: Suppose that the linear state system (5) and (6) is observable. Given any (n-p)-degree monic polynomial  $q(\lambda)$ , there exists gain H such that the reduced-dimension observer defined by (8) has an error state (11) with characteristic polynomial  $q(\lambda)$ .

#### V. ESTIMATING THE OUTPUT

In the previous section, we showed how to obtain an estimate  $\hat{w} = \hat{x}_{\beta}$  of the nonobservable part  $x_{\beta}$  of x. In this section, we proceed in explaining how this theory can be used to produce an estimate  $\hat{g}$  of the actual output vector g. Note that if the output itself is a state variable, then it is treated as nonobservable in order to produce its estimate.

According to (1), an estimate of g is given by

$$\hat{q} = C_e \hat{x} + D_e u \tag{14}$$

where  $\hat{x}$  is an estimate of the state-variable vector,  $C_e = C$ , and  $D_e = D$ . The proposed concurrent-error-detection method relies in realizing the above expression of  $\hat{g}$  with additional hardware. The resulting circuit is referred to as the estimator. In order to realize an estimate of g, it is required to estimate all the nonobservable state variables that appear in the expression  $C_e x$ . The linear system that describes the estimator can be derived by setting  $\hat{w} = \hat{x}_{\beta}$  and combining (8) and (14)

$$\dot{x}_{\gamma} = Hx_{\gamma} + Kx_{\alpha} + \Gamma u$$

$$\hat{g} = (C_e P)_{\beta} x_{\gamma} + [(C_e P)_{\alpha} + (C_e P)_{\beta} N] x_{\alpha} + D_e u \qquad (15)$$

where  $(C_eP)_{\alpha}$  and  $(C_eP)_{\beta}$  contain the first p and last n-p columns of  $C_eP$ , respectively.

$^1$ A matrix H is exponentially stable if there exist positive constants  $\mu$  and  $\lambda$  such that:

$$\|\mathbf{e}^{Ht}\| \le \mu \mathbf{e}^{-\lambda t} \qquad \forall t \ge 0.$$

$^2$ The n-dimensional time-invariant system (5) and (6) is observable if and only if

$$\operatorname{rank} \left[ \begin{array}{c} YP \\ YPA \\ \vdots \\ YPA^{n-1} \end{array} \right] = n.$$

Other equivalent definitions may also be listed [11]; for example, one may consider the eigenvalue test given in the Appendix.

#### VI. ERROR DETECTION

In the absence of permanent faults or transient errors, the difference  $g - \hat{g}$  converges exponentially to 0

$$g - \hat{g} = C(x - \hat{x})$$

$$= CP \begin{bmatrix} 0 \\ e_{\beta} \end{bmatrix}$$

$$\leq \mu CP \begin{bmatrix} 0 \\ e^{-\lambda t} \end{bmatrix} \to 0, \quad t \to \infty.$$

(16)

In the following, we show that the difference  $g-\hat{g}$  diverges from 0 if a fault is present either in the circuit or in the estimator, or if a transient error occurs. First, we discuss the case of permanent faults.

Possible component variations in the circuit appear as additive perturbations in the elements of the time-invariant matrices in (1). We group these perturbations in the difference matrices  $\Delta A, \, \Delta B, \, \Delta C, \, \text{and} \, \Delta D.$  Dropping squares of difference matrices and for a sufficiently large  $t_0$ , such that  $\Phi_H(t,0) \approx 0$ ,  $\forall t \geq t_0$ , it can be shown that, for  $t \geq t_0$ , the difference  $g - \hat{g}$  under process variations becomes

$$g - \hat{g} = (CP)_{\beta} \int_{0}^{t} \Phi_{H}(t, \tau) Q \vec{f}(\tau) d\tau + T \vec{f}(\tau)$$

(17)

where

$$Q = [-N \quad I]P^{-1}[\Delta A \quad \Delta B]$$

$$T = [\Delta C \quad \Delta D]$$

and

$$\vec{f}(\tau) = [x \quad u]^{\mathrm{T}}.$$

Similarly, let  $\Delta H$ ,  $\Delta K$ ,  $\Delta N$ ,  $\Delta \Gamma$ ,  $\Delta C_e$ , and  $\Delta D_e$  denote the discrepancies in the matrices that correspond to the estimator. Then, (17) can be rewritten to include process variations within the estimator as

$$g - \hat{g} = (CP)_{\beta} \int_{0}^{t} \Phi_{H+\Delta H}(t,\tau) Q \vec{f}(\tau) d\tau + T \vec{f}(\tau) + v$$

(18)

where

$$\upsilon = -(CP)_{\beta} \int_{0}^{t} \Phi_{H+\Delta H}(t,\tau) Q^{*} \vec{f}^{*}(\tau) d\tau$$

$$+ T' \vec{f}(\tau) + \Phi_{H+\Delta H}(t,0) e_{\beta}(0)$$

$$Q^{*} = \begin{bmatrix} \Delta N & 0_{(n-p)\times(n-p)} & \Delta (K-HN) & \Delta H & \Delta \Gamma \end{bmatrix}$$

$$T' = [\Delta C_{e} & \Delta D_{e}]$$

and

$$\vec{f}^*(\tau) = [P^{-1}\dot{x} \quad P^{-1}x \quad u]^{\mathrm{T}}.$$

From the expression of Q, it can be seen that if N has nonzero columns, then all component deviations in the circuit and the estimator are represented in the expression of  $g-\hat{g}$ . Therefore, the circuit-estimator scheme has the capability to indicate its own faults through a nonzero  $g-\hat{g}$ .

Special attention must be paid in the case where the circuit under test can be partitioned in a cascade of stages. In particular, if the input of a stage is included in the observable part  $x_{\alpha}$  of x, then all information processed from previous stages will be redundant and, thus, will be canceled out in the construction of  $\hat{g}$ . As a result, component deviations in previous stages will not be represented in the difference  $g-\hat{g}$ . A remedy to this problem is to avoid including the connection nodes between stages in the set of observable states or to apply the method separately for each stage.

With regards to transient errors, we can only give a qualitative argument. Such errors inject a charge on a node that temporarily alters the response of the circuit. If the output is affected, then at least one state variable that contributes to the construction of  $\hat{g}$  is also affected. Therefore, there is an inconsistency in the state variables with respect to the nominal case. Since the circuit and the estimator are inherently different, they process this inconsistency distinctly. In other words, the estimator is designed to follow the actual output only in an error-free scenario. When a transient error occurs, the estimator behavior is uncorrelated. Thus, it is expected that the difference  $g - \hat{g}$  will deviate from 0.

### VII. SELF-CHECKING PROPERTY

Often, there exist components that do not play a role in the formation of the output response for some inputs. For instance, a component might be inactive for a specific bandwidth. If its value deviates when the circuit operates in a frequency within this particular bandwidth, then the state vector still evolves as in the nominal case. Thus, the estimator does not "comprehend" the deviation and the difference  $g - \hat{g}$  remains 0. In terms of the  $g - \hat{g}$  expression in (17), this behavior is attributed to the multiplication of Q by the transition matrix of H within the integral. The transition matrix cancels out process variations that do not have an impact on the nominal operation. On the other hand, if a component in the circuit is inactive, then there must be a respective component in the estimator that is also inactive. Similarly, any deviations in this component do not contribute to the formation of  $\hat{g}$ , but instead are nullified by the multiplication of  $Q^*$  by  $\Phi_{H+\Delta H}(t,\tau)$  within the integral that appears in the expression of v.

Therefore, the circuit-estimator system is fault secure, that is, a fault will either be indicated through a nonzero difference  $g-\hat{g}$  or will not affect  $g-\hat{g}$  at all. Moreover, for every component, there exists an input signal that compels the difference  $g-\hat{g}$  to decisively depend on it. Thus, the system is also selftesting, that is, for every fault, there exists an input signal that generates a nonzero  $g-\hat{g}$ . The above two properties make the circuit-estimator system TSC. More details on these properties can be found in [12]. In order to ensure the TSC property for the entire error-detection scheme, we need to ensure that the analog checker is strongly code disjoint, that is, after the occurrence

of a fault within the checker, either the checker indicates it or retains its ability to assess the difference  $g - \hat{g}$  correctly. As discussed in [13], this is typically done by a periodic off-line test phase for the checker.

# VIII. ESTIMATOR SIZE

The estimator can be realized as an active linear circuit that monitors the input of the circuit under test and a subset of the observable internal nodes. In particular, the solution of (15) in the frequency domain is

$$\hat{g} = \left[ (CP)_{\alpha} + (CP)_{\beta} \left( (sI - H)^{-1} K + N \right) \right] x_{\alpha}$$

$$+ \left[ (CP)_{\beta} \left( sI - H \right)^{-1} \Gamma + D \right] u. \quad (19)$$

The matrix  $(sI - H)^{-1}$  can be written as

$$(sI-H)^{-1} = \frac{\operatorname{adj}(sI-H)}{|sI-H|}$$

where  $\operatorname{adj}(sI - H)$  is the adjoint matrix and  $|\cdot|$  denotes the determinant. |sI - H| is an (n - p)-degree polynomial in s. Thus, the order of the estimator equals, at most, the number of state variables that are estimated. This is a very useful result since the upper order of the estimator can be deduced by simple observation of the circuit. It also indicates the potential of the proposed method: Usually, observable nodes exist in the internal stages and, hence, the order of the estimator will be lower than that of a duplicate of the circuit under test. Lower order generally implies smaller area overhead and less complexity. Moreover, in the worst case scenario where none of the internal nodes is observable and only the input is available, (15) reduces to (1). In other words, the estimator becomes a duplicate of the examined circuit. An example for which our method does not have any advantages over duplication is the Sallen-Key biquad. In Sections X-A and X-B, we present two examples where it is sufficient to estimate only one state variable. It is also likely that some poles of the transfer functions in (19) are canceled by zeros due to inherent symmetries. In this case, the order of the estimation circuit is less than n-p. In Section X-C, we present a third example where five out of eight state variables need to be observed, yet the order of the resulting estimation circuit is only three.

As a last remark, since we are interested in an estimator that occupies minimal area, one should consider observing even nonobservable states by inserting additional buffers in the design [14]. The cost efficiency of using such test-point structures depends on the hardware that can be potentially saved, as compared to estimating these nonobservable states.

#### IX. ANALOG-CHECKER CONSIDERATIONS

The proposed concurrent-error-detection method relies on examining the difference  $g-\hat{g}$ , which ideally is 0 in the absence of errors. Yet, due to mismatches and other nonidealities, the comparison cannot be made exact. Rather, it should reflect the correlation between the encoded signals. For this purpose, the absolute difference  $|g-\hat{g}|$  is compared to a threshold

TABLE I

TOTAL RESISTANCE AND CAPACITANCE OF THE CIRCUIT UNDER TEST

AND ITS ESTIMATION CIRCUIT

|                  | biquadratic |        | leapfrog |        | butterworth |        |

|------------------|-------------|--------|----------|--------|-------------|--------|

|                  | circ.       | estim. | circ.    | estim. | circ.       | estim. |

| $R (in K\Omega)$ | 85          | 42     | 130      | 47     | 807.77      | 385.44 |

| C (in nF)        | 40          | 20     | 60       | 10     | 63.52       | 43     |

| # op-amps        | 3           | 2      | 6        | 3      | 6           | 4      |

$V_{\delta}>0$  in order to realize a tolerance window within which the two signals are deemed equal.  $V_{\delta}$  is chosen so that the probability of false alarms, both positive and negative, is minimized. Its optimal value can be found on the basis of a worst case tolerance analysis [15], which aims to identify the worst case parameter sets.  $V_{\delta}$  depends on both the frequency and the magnitude of the evaluated signals

$$V_{\delta} = V_{\delta}(\omega, g, \hat{g}). \tag{20}$$

Accurate threshold assignment is a common problem among existing analog test solutions [16]. Essentially, any threshold establishes an inherent bias when evaluating a signal pair and, thus, the probability of false alarms can be minimized but cannot be eliminated. This happens because  $V_{\delta}$  accounts for the probability of nominal process drifts in the circuit under test and the checker itself. Since the magnitude of these nonideal effects is not known *a priori*, the assignment of  $V_{\delta}$  inevitably introduces a bias towards accepting or rejecting a signal pair.

Analog checkers that have the ability to adjust their threshold to the input pair magnitude have been presented in [17] and [18]. These checkers provide better moderation of the bias as compared to other solutions that implement a constant threshold [13]. They implement a threshold that is defined as a percentage of the absolute average value of the input signals, plus a small constant  $V_{\delta,\min}$ , which accounts for nominal offsets

$$V_{\delta} = \varepsilon_r \frac{|g + \hat{g}|}{2} + V_{\delta, \min}.$$

(21)

The constant  $\varepsilon_r$  can be chosen to achieve the highest possible accuracy in the bandwidth of interest.

#### X. EXPERIMENTAL RESULTS

In this section, we demonstrate the various points of the developed concurrent-error-detection methodology on three linear analog filters, a biquadratic, a leapfrog lowpass, and a Butterworth bandpass. The circuits are breadboarded to prove the practical viability of the method. If the initial condition of the error differential equation (11) is 0, i.e.,  $e_{\beta}(t=0)=0$ , the estimate converges to the output value immediately. In order to impose a nonzero initial condition on the differential equation and demonstrate the exponential reduction of  $g-\hat{g}$ , we insert switches at some inputs of the estimation circuit, which we turn ON at an arbitrarily chosen time  $t_{\rm o}$ . The experiments illustrate the following.

Estimator area: In all cases, the derived estimator is simpler than a duplicate of the circuit. As shown in Table I, the reduction in the total resistance and capacitance is, in most cases, more than 50%.

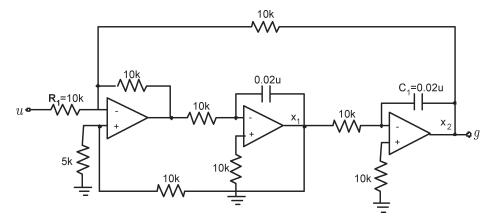

Fig. 2. Biquadratic filter.

- 2) Error-free case: In error-free operation, the estimate converges exponentially to the output value. Since the input space is infinite, we illustrate this convergence for arbitrarily chosen inputs.

- 3) Faulty conditions: The estimate fails to converge to the output value in the presence of errors. We present measurements in the presence of faults in the monitored circuit and the estimator as well as a measurement that shows the response to a transient error.

- 4) Convergence speed: Regarding the biquadratic and the leapfrog filters, a single state variable needs to be estimated. Hence, H reduces to a scalar, which equals the inverse of the time constant of the exponential decay. Regarding the bandpass filter, five state variables need to be estimated. Hence, the dominant time constant is the inverse of the largest eigenvalue of H. In order to illustrate the impact of H on the rate of convergence, we choose the largest eigenvalue of H in the third example to be largely different than the scalar H in the first two examples.

We emphasize that the proposed method does not rely on a prescribed fault model. Rather, it detects any malfunction that leads to an unacceptably large discrepancy between the circuit output and the estimate. The magnitude of the detection threshold depends on the specific application and data collected from the manufacturing process.

#### A. Biquadratic Filter

A Biquadratic filter is shown in Fig. 2. This circuit has two state variables. The state-variable equation can be formulated as

$$\dot{x} = \begin{bmatrix} -\frac{1}{CR} & \frac{1}{CR} \\ -\frac{1}{CR} & 0 \end{bmatrix} x + \begin{bmatrix} \frac{1}{CR} \\ 0 \end{bmatrix} u$$

where  $x=[x_1 \quad x_2]^{\rm T}$ ,  $R=10~{\rm k}\Omega$ , and  $C=0.02~{\rm \mu}{\rm F}$ . All state variables are observable. The lowpass output can be expressed as  $g=Cx=[0\quad 1]x=x_2$ . Therefore, the problem reduces to estimation of  $x_2$  by monitoring  $x_1$  and  $x_2$ . The reduced-

Fig. 3. Estimation circuit for the biquadratic filter.

size state-variable vector is  $x_{\alpha} = \begin{bmatrix} 1 & 0 \end{bmatrix} x$  and, thus, the transformation matrix  $P^{-1}$  is simply the identity. This yields

$$F = \begin{bmatrix} -5000 & 5000 \\ -5000 & -100 \end{bmatrix}, \quad G = \begin{bmatrix} 0 \\ 5000 \end{bmatrix}.$$

Hence, the necessary conditions for the output of the observer in (8) to exponentially converge to  $x_2$  are

$$H = -5000N < 0$$

$K = -5000 + 5000N + HN$

$\Gamma = -5000N$ .

Choosing N=1 yields  $H=K=\Gamma=-5000$ . From (19), we obtain the following estimate:

$$\hat{g} = \frac{s}{s + 5000} x_1 - \frac{5000}{s + 5000} u.$$

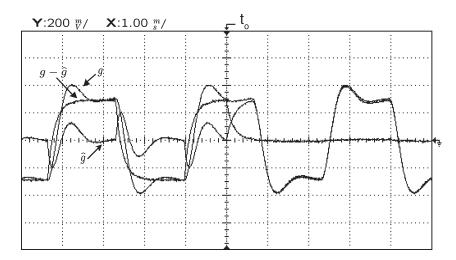

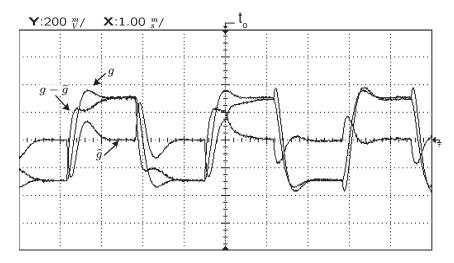

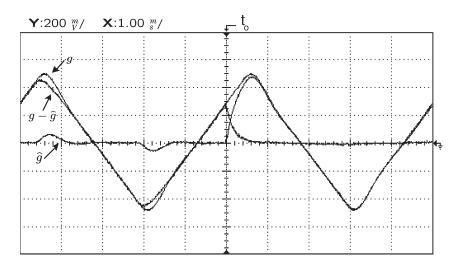

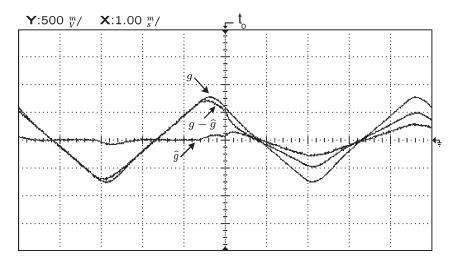

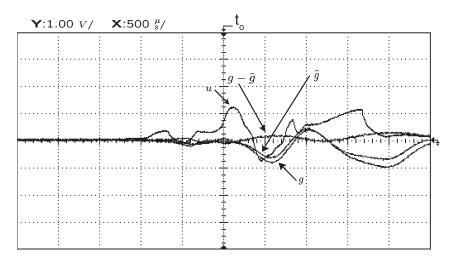

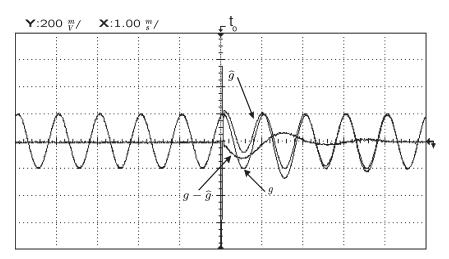

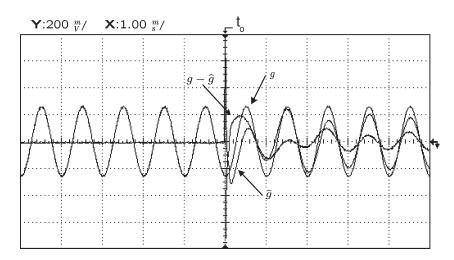

This function can be implemented by the active circuit shown in Fig. 3. The estimator is activated at  $t=t_{\rm o}$  so that  $e_{\beta}(t=t_{\rm o})\neq 0$ . For  $t< t_{\rm o}$ , its input u is disconnected from the input of the biquadratic filter and, thus, the estimate is not constructed properly. Fig. 4 illustrates the exponential convergence in the fault-free case for a square-wave input signal at a low frequency of the passband. The measurement is repeated for a faulty value of 15 nF for the capacitor  $C_1$ . The result is shown in Fig. 5. Due to this fault, the estimate never converges to the output of the circuit. Fig. 6, illustrates the exponential convergence for an arbitrary aperiodic input signal u. The measurement is repeated in Fig. 7 for  $R_1=15~{\rm k}\Omega$ . Due to this fault, the estimate diverges.

Fig. 4. Estimation converges in the absence of faults.

Fig. 5. Estimation fails to converge in the case of a faulty value of 15 nF for the capacitor  $C_1$ .

Fig. 6. Estimation converges in the absence of faults.

Fig. 7. Estimation fails to converge in the case of a faulty value of 15 k $\Omega$  for the resistor  $R_1$ .

Fig. 8. Leapfrog lowpass filter.

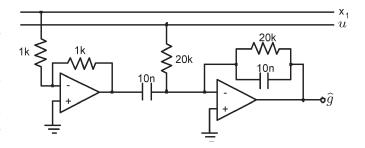

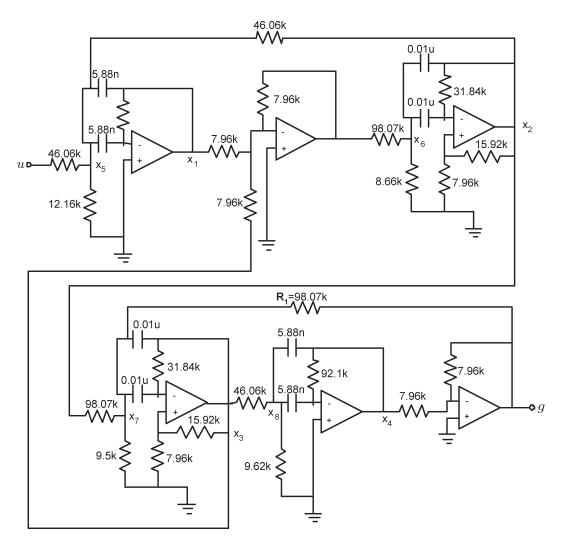

## B. Leapfrog Lowpass Filter

The second example is a leapfrog lowpass filter, shown in Fig. 8. There are six state variables, one of which is the output itself,  $g=x_6$ . Moreover, note that  $x_2=-x_1-x_4$  and  $x_5=-x_4$ . Hence, if we choose  $x=\begin{bmatrix}x_1&x_3&x_4&x_6\end{bmatrix}^T$ , the state-variable equation is

$$\dot{x} = \begin{bmatrix} -\frac{1}{RC_1} & -\frac{1}{RC_1} & 0 & 0\\ -\frac{1}{RC_2} & 0 & \frac{1}{RC_2} & 0\\ 0 & -\frac{1}{RC_2} & 0 & -\frac{1}{RC_2}\\ 0 & 0 & \frac{1}{RC_1} & \frac{1}{RC_1} \end{bmatrix} x + \begin{bmatrix} -\frac{1}{RC_1}\\ 0\\ 0\\ 0 \end{bmatrix} u$$

where  $R=10~{\rm k}\Omega,~C_1=10~{\rm nF},$  and  $C_2=20~{\rm nF}.$  We will estimate g by monitoring  $x_1,x_3,x_4,$  and u. Hence, the reduced-size state-variable vector is specified as

$$x_{\alpha} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} x.$$

Again, the transformation matrix  $P^{-1}$  is the identity. Thus,

$$F = \begin{bmatrix} -10^4 & -10^4 & 0 & 0 \\ -5 \cdot 10^3 & 0 & 5 \cdot 10^3 & 0 \\ 0 & -5 \cdot 10^3 & 0 & -5 \cdot 10^3 \\ 0 & 0 & 10^4 & 10^4 \end{bmatrix}$$

$$G = \begin{bmatrix} -10^4 \\ 0 \\ 0 \\ 0 \end{bmatrix}.$$

If we denote by  $N_i$ , i = 1, 2, 3, the elements of the  $1 \times 3$  matrix N, the conditions for exponential convergence become

$$H = -10^{4} + 5000N_{3} < 0$$

$$K = \left[ \frac{N_{3}N_{1} - N_{2}}{2 \cdot 10^{-4}} \quad \frac{N_{1} - N_{2}}{10^{-4}} + \frac{N_{3}(N_{2} + 1)}{2 \cdot 10^{-4}} \quad \frac{1 - N_{3}}{10^{-4}} + \frac{N_{3}^{2} - N_{2}}{2 \cdot 10^{-4}} \right]$$

$$\Gamma = 10^{4}N_{1}.$$

Hence, choosing  $N_3 = 1$ ,  $N_1 = N_2 = -1$ , we obtain

$$H = -5000$$

$K = [0 \quad 0 \quad 10^4]$

$\Gamma = -10^4$ .

From (19), the estimate for the output is

$$\hat{g} = \hat{x}_6 = \frac{10^4}{s + 5000} x_5 - \frac{10^4}{s + 5000} u - x_1 - x_3 - x_5.$$

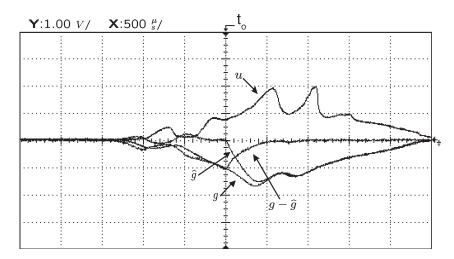

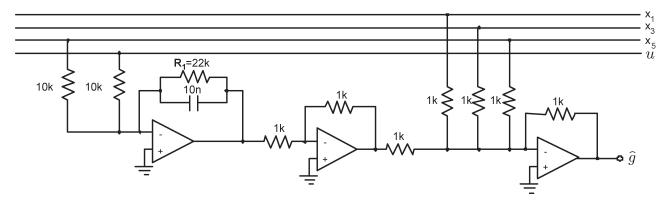

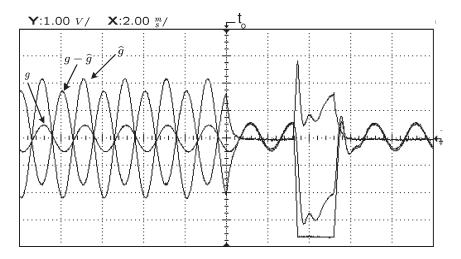

The estimation circuit is shown in Fig. 9. Fig. 10 illustrates the convergence for a triangular input wave within the passband, when all components have nominal values. Once again, we utilize switches that we turn ON at  $t=t_{\rm o}$  to impose random initial conditions. Since the value of H in this example is the

Fig. 9. Estimation circuit for the leapfrog lowpass filter.

Fig. 10. Estimation converges in the absence of faults.

Fig. 11. Estimation fails to converge in the case of a faulty value of  $22 \text{ k}\Omega$  for the resistor  $R_1$ .

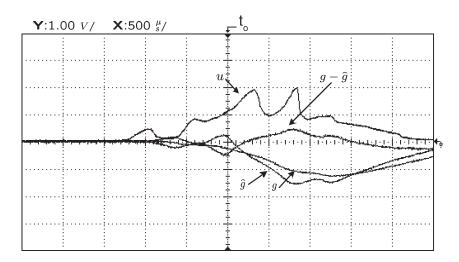

same as in the previous one, convergence is achieved with the same time constant. Fig. 11 shows that the estimate fails to converge when resistor  $R_1$  in the estimation circuit takes a faulty value of  $22~\mathrm{k}\Omega$ . Fig. 12 illustrates the convergence for an arbitrary aperiodic input u. In this case, convergence is faster than in the cases shown in Figs. 4, 6, and 10 since the initial error  $e_\beta(t=t_\mathrm{o})$  is very small. Fig. 13 shows that the estimate

fails to converge for this random input when resistor  $R_2$  in the filter takes a faulty value of 15 k $\Omega$ .

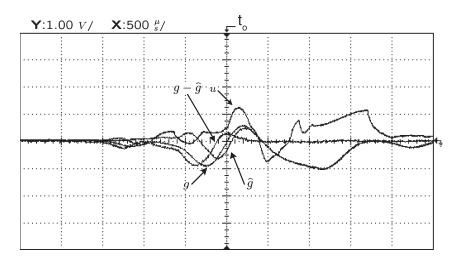

Fig. 14 illustrates the respective responses in the occurrence of a transient error. A short pulse is added to the signal of a randomly selected node at around  $t_{\rm o}+4$  ms. The invariant difference  $\hat{g}-g$  becomes temporarily nonzero and decreases exponentially to 0 again.

Fig. 12. Estimation converges in the absence of faults.

Fig. 13. Estimation fails to converge in the case of a faulty value of 15 k $\Omega$  for the resistor  $R_1$ .

Fig. 14. Estimation diverges temporarily in the occurrence of a transient error.

## C. Butterworth Bandpass Filter

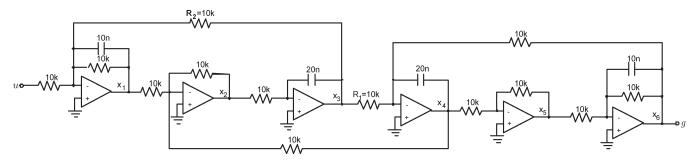

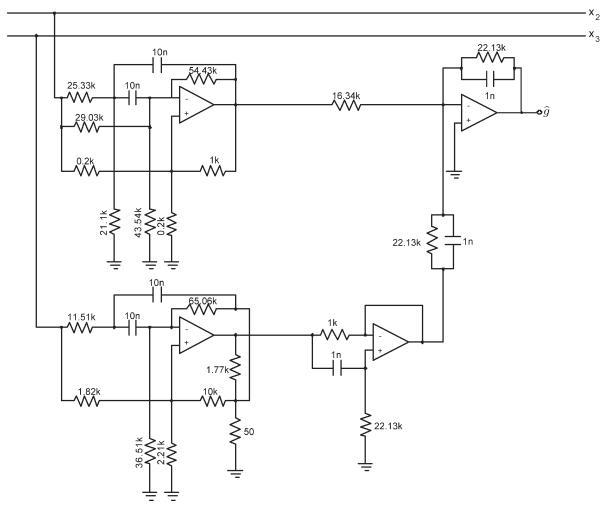

As a third example, we designed the error-detection circuit of a Butterworth bandpass filter, shown in Fig. 15. The circuit has eight state variables, only four of which are observable. The output can be written as  $g=-x_4$ . Hence, in this case, we need

to estimate the four nonobservable state variables,  $x_5$ ,  $x_6$ ,  $x_7$ ,  $x_8$ , as well as  $x_4$ . A step-by-step illustration of the method is avoided here because of the large-sized matrices. The largest eigenvalue of the chosen H is  $\lambda_m = -828.65$ .

Fig. 15. Butterworth bandpass filter.

The estimation circuit is shown in Fig. 16. The biquadratic functions are implemented by the single-amplifier general biquad [19]. The convergence in the error-free case for a sinusoidal input signal is shown in Fig. 17. Switches are inserted in the signal paths of both inputs of the estimation circuit and, thus, for  $t < t_{\rm o}$ , its output is 0. In this example, H is a matrix and, thus, the difference  $g - \hat{g}$  is contained within an exponential decay, as (13) suggests. As it can be seen, since  $\lambda_m$  is larger than the scalar H in the previous examples, convergence is slower. Finally, Fig. 18 shows that the estimate fails to converge when resistor  $R_1$  takes a faulty value of 75 k $\Omega$ , causing an error at the output of the circuit.

#### XI. CONCLUSION

We presented a rigorous concurrent-error-detection methodology for linear analog circuits. Our approach relies on estimating the response of the circuit by means of information available at observable nodes and comparing the estimate to the circuit response. The estimate matches the output only in the error-free case and diverges otherwise. By and large, this approach results in an error-detection circuit that is smaller than a duplicate of the examined circuit. By construction, the invariant signal spans the entire parameter space of the circuit and is

monitored continuously. Response correctness information is obtained at the operational speed for any input value and for the entire frequency spectrum. Hence, concurrent detection of both transient errors and permanent faults is ensured. The various points of this method were demonstrated through representative experiments on three linear analog filters.

#### **APPENDIX**

The proof is based on three well-known results in linear system theory [11], [20], which are stated in Theorems 2–4.

Theorem 2: For every n-dimensional controllable pair (A,B) and each symmetric set of complex numbers  $\Lambda$ , there exist a matrix L such that

spectrum

$$(A + BL) = \Lambda$$

.

Theorem 3: A pair (C,A) is observable if and only if for every complex scalar  $\nu$  the only complex  $n \times 1$  vector  $\zeta$  that satisfies

$$A\zeta = \nu\zeta, \quad C\zeta = 0$$

is  $\zeta = 0$ .

The next theorem follows directly from Theorem 3.

Fig. 16. Estimation circuit for the Butterworth bandpass filter.

Fig. 17. Estimation converges in the absence of faults.

Theorem 4: A pair (C, A) is observable if and only if

$$\operatorname{rank} \begin{bmatrix} C \\ \nu I - A \end{bmatrix} = n$$

This observability test criterion need only be applied for those values of  $\nu$  that are eigenvalues of A.

We need to prove that there exists  $H = F_{22} - N F_{12}$  such that

$$|\lambda I - (F_{22} - NF_{12})| = q(\lambda). \tag{22}$$

Fig. 18. Estimation fails to converge in the case of a faulty value of 75 k $\Omega$  for the resistor  $R_1$ .

Equivalently, noticing that  $(F_{22}-NF_{12})^{\mathrm{T}}=F_{22}^{\mathrm{T}}-F_{12}^{\mathrm{T}}N^{\mathrm{T}}$ , (22) becomes

$$|\lambda I - (F_{22}^{\mathrm{T}} - F_{12}^{\mathrm{T}} N^{\mathrm{T}})| = q(\lambda).$$

(23)

According to theorem 2, it is adequate to show that the pair  $(F_{22}^{\rm T},F_{12}^{\rm T})$  is controllable. If  $(F_{22}^{\rm T},F_{12}^{\rm T})$  is controllable, then there exists a matrix N such that (23) is satisfied. However, we know that controllability of  $(F_{22}^{\rm T},F_{12}^{\rm T})$  is equivalent to the observability of  $(F_{12},F_{22})$ . Hence, it is adequate to show that the (n-p)-dimensional linear state equation

$$\dot{x} = F_{22}x$$

$$g = F_{12}x$$

(24)

is observable. Supposing the contrary, a contradiction is obtained as follows. If (24) is not observable, then by Theorem 3, there exists a nonzero  $(n-p)\times 1$  vector  $\zeta$  and a complex scalar  $\nu$  such that

$$F_{22}\zeta = \nu\zeta, \quad F_{12}\zeta = 0.$$

(25)

Therefore,

$$\begin{bmatrix} F_{11} & F_{12} \\ F_{21} & F_{22} \end{bmatrix} \begin{bmatrix} 0_{p \times 1} \\ \zeta \end{bmatrix} = \begin{bmatrix} F_{12}\zeta \\ F_{22}\zeta \end{bmatrix} = \nu \begin{bmatrix} 0_{p \times 1} \\ \zeta \end{bmatrix}$$

(26)

And

$$\begin{bmatrix} I_p & 0 \end{bmatrix} \begin{bmatrix} 0_{p \times 1} \\ \zeta \end{bmatrix} = 0. \tag{27}$$

The above two equations can be written in matrix form

$$\begin{bmatrix} I_p & 0\\ \nu I - F \end{bmatrix} \begin{bmatrix} 0_{p \times 1}\\ \zeta \end{bmatrix} = 0. \tag{28}$$

Hence,

$$\operatorname{rank} \begin{bmatrix} I_p & 0 \\ \nu I - F \end{bmatrix} < n. \tag{29}$$

By theorem 4, the linear system (5) and (6) is not observable, which is a contradiction to the observability hypothesis. This completes the proof.

#### REFERENCES

- [1] B. Vinnakota, *Analog and Mixed-Signal Test*. Englewood Cliffs, NJ: Prentice-Hall, 1998.

- [2] M. Lubaszewski, S. Mir, A. Rueda, and J. L. Huertas, "Concurrent error detection in analog and mixed-signal integrated circuits," in *IEEE* 38th Midwest Symp. Circuits and Systems, Rio de Janeiro, Brazil, 1996, pp. 1151–1156.

- [3] J. L. Huertas, A. Rueda, and D. Vasquez, "Testable switched-capacitor filters," *IEEE J. Solid-State Circuits*, vol. 28, no. 7, pp. 719–724, Jul. 1993.

- [4] A. Chatterjee, "Concurrent error detection and fault-tolerance in linear analog circuits using continuous checksums," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 1, no. 2, pp. 138–150, Jun. 1993.

- [5] H. Yoon, A. Chatterjee, and L. A. Hughes, "Optimal design of checksum-based checkers for fault detection in linear analog circuits," in *IEEE Int. Conf. VLSI Design*, Hyderabad, India, 1997, pp. 393–397.

- [6] Y. Zhou, M. W. T. Wong, and Y. Min, "Hardware reduction in continuous check-based analog checkers: Algorithm and its analysis," *J. Electron. Test.*, vol. 9, no. 1–2, pp. 153–163, 1996.

- [7] A. Chatterjee and M. A. D'Abreu, "The design of fault-tolerant linear digital state variable systems: Theory and techniques," *IEEE Trans. Comput.*, vol. 42, no. 7, pp. 794–808, Jul. 1993.

- [8] C. N. Hadjicostis, "Nonconcurrent error detection and correction in fault-tolerant discrete-time LTI dynamic systems," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 50, no. 1, pp. 45–55, Jan. 2003.

- [9] E. Simeu, A. W. Peters, and I. Rayane, "Automatic design of optimal concurrent fault detector for linear analog systems," in *IEEE Int. Symp. Fault-Tolerant Computing*, Madison, WI, 1999, pp. 184–191.

- [10] S. Ozev and A. Orailoglu, "Design of concurrent test hardware for linear analog circuits with constrained hardware overhead," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 12, no. 7, pp. 756–765, Jul. 2004.

- [11] W. J. Rugh, *Linear System Theory*, 2nd ed. Englewood Cliffs, NJ: Prentice-Hall, 1996.

- [12] M. Nicolaidis, "Finitely self-checking circuits and their application on current sensors," in *IEEE VLSI Test Symp.*, Atlantic City, NJ, 1993, pp. 66–69.

- [13] V. Kolarik, M. Lubaszewski, and B. Courtois, "Designing self-exercising analog checkers," in *IEEE VLSI Test Symp.*, Cherry Hill, NJ, 1994, pp. 252–257.

- [14] C. L. Wey, "Built-in self-test (BIST) structure for analog circuit fault diagnosis," *IEEE Trans. Instrum. Meas.*, vol. 39, no. 3, pp. 517–521, Jun. 1990.

- [15] M. W. Tian and C.-J. R. Shi, "Worst case tolerance analysis of linear analog circuits using sensitivity bands," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 47, no. 8, pp. 1138–1145, Aug. 2000.

- [16] S. Sunter and N. Nagi, "Test metrics for analog parametric faults," in IEEE VLSI Test Symp., Dana Point, CA, 1999, pp. 226–234.

- [17] V. Kolarik, S. Mir, M. Lubaszewski, and B. Courtois, "Analog checkers with absolute and relative tolerances," *IEEE Trans. Comput. Aided Des. Integr. Circuits Syst.*, vol. 14, no. 5, pp. 607–612, May 1995.

- [18] H. G. D. Stratigopoulos and Y. Makris, "An analog checker with inputrelative tolerance for duplicate signals," J. Electron. Test.: Theory Appl., vol. 20, no. 5, pp. 479–488, 2004.

- [19] J. J. Friend, C. A. Harris, and D. Hilberman, "STAR: An active biquadratic filter section," *IEEE Trans. Circuits Syst.*, vol. CAS-22, no. 2, pp. 115– 121, Feb. 1975.

- [20] P. J. Antsaklis and A. N. Michel, *Linear Systems*. New York: McGraw-Hill, 1997.

Haralampos-G. D. Stratigopoulos (S'02) was born in Greece in 1978. He received the Diploma of electrical and computer engineering from The National Technical University of Athens, Greece, in 2001 and the M.S. degree in electrical engineering from Yale University, New Haven, CT, in 2003. He is currently pursuing the Ph.D. degree in electrical engineering at Yale University.

His research interests include analog circuit testing and design, pattern recognition, and modeling of the MOS transistor.

**Yiorgos Makris** (S'99–A'01–M'03) received the Diploma of computer engineering and informatics from the University of Patras, Greece, in 1995, and the M.S. and Ph.D. degrees in computer science and engineering from the University of California, San Diego, in 1997 and 2001, respectively.

He is currently an Associate Professor of Electrical Engineering and Computer Science at Yale University, New Haven, CT, where he leads the Testable and Reliable Architectures (TRELA) Research Group. His research interests include test

and reliability of digital and analog circuits and systems.