# Phase Noise Reduction in LC VCO's Using an Array of Cross-Coupled Nanoscale MOSFETs and Intelligent Post-Fabrication Selection

Pavan Yelleswarapu<sup>®</sup>, *Member, IEEE*, Amit Jha<sup>®</sup>, *Senior Member, IEEE*, Richard Willis, Yiorgos Makris<sup>®</sup>, *Senior Member, IEEE*, and Kenneth K. O<sup>®</sup>, *Fellow, IEEE*

Abstract-Low-frequency noise, thermal noise, and dc characteristics of nanoscale MOS transistors with dimensions close to the process minimum are highly variable. This article demonstrates a phase noise (PN) reduction technique for LC voltage-controlled oscillators (VCOs) that use an intelligent postfabrication selection of a subset of an array of near minimum-size cross-coupled transistor pairs with reduced low-frequency noise and thermal noise. Using the technique, the PN of a VCO is lowered from the maximum by 3.5 dB at 600-kHz, 1-MHz, and 3-MHz offsets from a 3.8-GHz carrier. The lowest PN of -122, -129, and -139.5 dBc/Hz at 600-kHz, 1-MHz, and 3-MHz offsets, respectively, from a 3.8-GHz carrier has been measured using the PLL method of the Keysight E5052B Signal Source Analyzer. The VCO prototype was fabricated in a 65-nm CMOS process and dissipates 7 mW of dc power. The maximum figure of merit (FoM), including PN, carrier frequency, and power consumption, is 193 dBc/Hz, and the FoM, including the VCO core area, FoM<sub>A</sub>, is 209 dBc/Hz.

*Index Terms*—CMOS, defects, genetic algorithm, LC, low-frequency noise, phase noise (PN), post-fabrication selection, thermal noise, transistor array, variability, voltage-controlled oscillators (VCO).

#### I. INTRODUCTION

VOLTAGE-CONTROLLED oscillator (VCO) is a key building block in high-performance wireless and wireline communication systems. The phase noise (PN) of VCOs impacts the system performance in numerous RF and millimeter-wave applications. Adjacent channel rejection, jitter, and error vector magnitude (EVM) of demodulated signals that depend on VCO PN are key factors determining the order of modulation that can be deployed for communication systems to increase the data rate and bandwidth efficiency.

Manuscript received December 23, 2021; revised March 11, 2022; accepted March 21, 2022. Date of publication April 19, 2022; date of current version June 3, 2022. This work was supported by the Semiconductor Research Corporation (SRC) through the Texas Analog Center of Excellence, The University of Texas at Dallas (Task ID: 2712.025). (*Corresponding author: Pavan Yelleswarapu.*)

Pavan Yelleswarapu is with Qualcomm Technologies Inc., Richardson, TX 75082 USA (e-mail: vxy130030@utdallas.edu).

Amit Jha is with Qualcomm Technologies Inc., San Jose, CA 95110 USA. Richard Willis is with Citigroup Global Markets Inc., New York, NY 11217 USA.

Yiorgos Makris and Kenneth K. O are with the Electrical and Computer Engineering Department, The University of Texas at Dallas, Richardson, TX 75080 USA.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TMTT.2022.3164949.

Digital Object Identifier 10.1109/TMTT.2022.3164949

For instance, the 3GPP TS 38.101-1 EVM requirements for a wireless receiver employing a 256-QAM modulation scheme for the emerging 5G communication are only 3.5% [1] and become even tighter as the order of modulation increases, which makes the PN and integrated jitter critical in millimeter-wave phased array systems [2], [3]. Similarly, in millimeter-wave radar applications, the low integrated jitter or a low PN of a VCO improves resolution and the probability of detection of radars [4].

To reduce the PN of LC VCOs, numerous circuit topologies have been reported [3]–[19]. The noise of the cross-coupled pair of transistors in CMOS LC VCOs is a major contributor to the overall PN. Upconversion of both the low-frequency noise and thermal noise of cross-coupled transistors is a key mechanism contributing to the PN of LC VCOs [5]–[21].

Scaling of the MOSFETs in advanced CMOS technologies accompanies increased process variation and noise variability. The number of intended dopants and unintended defects in a minimum-sized device is reduced with the technology scaling. One missing dopant or having an additional defect can have a dramatic impact on device characteristics, including threshold voltage, current, and low-frequency noise [22]–[26]. In addition, the thermal noise can also considerably vary due to the variations of the dc properties, such as mobility, effective channel length, threshold voltage, and gate dielectric layer thickness [27]–[29].

This article presents a PN reduction technique in LC VCOs by using an array of individually selectable cross-coupled pairs of transistors [30]. Applying an intelligent post-fabrication selection process [31], [32] in a VCO using the array to select cross-coupled pairs with reduced low-frequency noise and thermal noise, the PN is lowered from the average by 2 dB at 600-kHz and 1-MHz offsets and by 1.5 dB at a 3-MHz offset, respectively, from a 3.8-GHz carrier. It is also lowered by 3.5 dB from the maximum PN at the offset frequencies. The average and maximum PNs should be close to those for a conventional VCO using a cross-coupled pair formed with two transistors but with the same total width as that of the selected cross-coupled pairs in the array. The lowest PN of -122, -129, and -139.5 dBc/Hz at 600-kHz, 1-MHz, and 3-MHz offsets, respectively, from a 3.8-GHz carrier has been measured using the phase-locked loop (PLL) method without correlation and with an averaging of 50 in the Keysight E5052B Signal Source Analyzer.

0018-9480 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

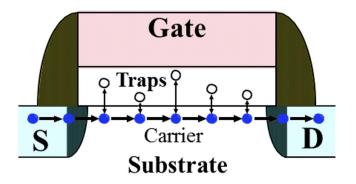

Fig. 1. Trapping-detrapping process in a gate dielectric layer of MOSFETs [34].

This article is an extension of work in [30] where the concept and some of the preliminary measurement results were introduced. This article by elimination: 1) demonstrates that the variation of observed PN is due to the low-frequency noise variation; 2) reports that the variation of thermal noise in near minimum-sized transistors can also be exploited to lower the PN; and 3) demonstrates the use of a more efficient algorithm for searching combinations with lower noise in high-dimensional unstructured spaces. Unlike the works in [31] and [32] that utilized the variation of static device parameters and post-fabrication selection to lower offsets, this work utilizes the variability of thermal noise and reduced low-frequency noise at the lower end of low-frequency noise distribution in near minimum-sized transistors with intelligent post-fabrication selection to lower the PN of 4-GHz VCOs.

This article is organized as follows. Sections II and III describe the variability of low-frequency and thermal noise in MOS transistors, respectively, and how these variabilities can be advantageously used to lower the PN of LC VCOs. Section IV presents the proposed VCO using an array of cross-coupled transistor pairs with size near the process minimum. Section V describes the intelligent-search genetic algorithm used for the post-fabrication selection. Finally, Section VI reports the measurement results before concluding.

### II. LOW-FREQUENCY NOISE VARIABILITY

The McWhorter model [33] attributes the trapping and detrapping processes of the channel electrons or holes in a gate oxide or dielectric region as the generation mechanism for low-frequency noise of MOSFETs, as shown in Fig. 1. The properties of traps determine the power spectral density (PSD) and corner frequency. The PSD of each individual trap, also called a Lorenztian that originates random telegraph noise (RTN), can be added to generate the 1/f-noise spectrum [33], [34]. Since the number of traps in a large area device is large, the low-frequency noise variation from device to device is reduced because the sum of all the PSDs averages the variations due to individual traps.

However, in nanoscale transistors, the number of traps in the Si-gate dielectric layer decreases to a few or less than one per transistor. Such transistors do not exhibit the 1/f-noise spectrum that requires averaging the effects of

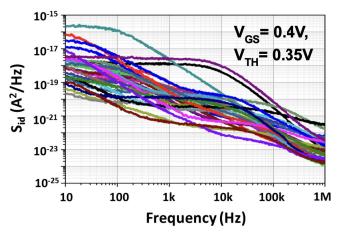

Fig. 2. Measured low-frequency noise variability of 32 nMOS transistors with dimensions near the minimum in a 65-nm CMOS process (W = 150 nm, L = 60 nm, and Area = 9000 nm<sup>2</sup>).

a large number of traps [35]–[39]. The defect density related to low-frequency noise in nanoscale CMOS is  $\sim 1 \times 10^9$  cm<sup>-2</sup> (kTN<sub>ot</sub>/ $\alpha_t$  of [23, eq. (1)]), which translates to on average, one trap in  $\sim 300 \times 300$  nm<sup>2</sup> or  $\sim 90\ 000$  nm<sup>2</sup>, which is larger than the area of minimum-sized transistors in nanoscale CMOS. In such MOSFETs, the number of traps is not a fixed process constant but rather a random variable whose uncertainty increases with a shrinking device size. This leads to a large variation of low-frequency noise for otherwise similar devices sized near the minimum. In addition, even if the number of traps is the same, the locations of traps in the dielectric layer can be different, which also results in dissimilar Lorenztians and, therefore, an increase in the low-frequency noise variation [35]–[39].

Fig. 2 shows the measured low-frequency noise of 32 nMOS transistors with a width and a length of 150 and 60 nm, respectively, or for a gate area of ~9000 nm<sup>2</sup>. The transistors are biased at  $V_{GS} = 0.4$  V,  $V_{DS} = 0.6$  V, and  $V_{TH} = ~0.35$  V. From the plot, it can be observed that the drain current noise spectral density varies by four orders of magnitude at 10 kHz and three orders of magnitude at 1 MHz. This large variation is attributed to the fact that the number of traps in the transistors is not the same, as well as to the fact that dc current varies due to the variation of transistor parameters, such as effective channel length, mobility, gate dielectric thickness, and threshold voltage [27]–[29]. The average low-frequency noise in the PDK is dominated by a few devices with the highest noise. In addition, some of the transistors can have noise significantly lower than the average low-frequency noise.

Fig. 3 shows the maximum and minimum current noise spectral densities of a set of ten transistors randomly selected from the array of 32 transistors. The minimum current noise spectral density is an order of magnitude lower than the normalized sum predicted by the PDK. This implies that, if only the transistors with low noise can be used by postfabrication selection, then it should be possible to significantly reduce the low-frequency noise impact. Using minimum-sized transistors to reduce the low-frequency noise is opposite

Fig. 3. Current noise PSD of combinations formed by randomly selecting ten transistors out of 32.

to the conventional approach of reducing the impact of low-frequency noise by using larger transistors, which relies on averaging the value determined by the PDK model. Because of this, the approach using post-fabrication selection can result in circuits with significantly reduced impact of low-frequency noise.

#### **III. THERMAL NOISE VARIABILITY**

The channel thermal noise of an MOS transistor operating in a saturation region can be modeled by a current source [40]. The current noise spectral density is

$$i_{n,d}^2 = 4kT\gamma g_{d0} \tag{1}$$

where  $g_{d0}$  is the zero-bias drain conductance of the device and  $\gamma$  is a bias-dependent coefficient of thermal noise, which can be much greater than one for short-channel MOS transistors [41]. The zero-bias drain conductance,  $g_{d0}$ , and the transconductance,  $g_m$ , are related by the factor  $\alpha$  [41], as shown in the following equations:

$$\alpha \triangleq \frac{g_m}{g_{d0}}.$$

(2)

For short-channel MOS transistors,  $\alpha$  can be much less than one. It is well known that  $g_m$  in terms of bias voltages  $(V_{\text{GS}}, V_{\text{DS}})$ , threshold voltage  $(V_{\text{TH}})$ , width (W), length (L), mobility  $(\mu_n)$ , and gate capacitance  $(C_{\text{ox}})$  of a long-channel MOS transistor is

$$g_m = \mu_n C_{\rm ox} \left(\frac{W}{L}\right) (V_{\rm GS} - V_{\rm TH}) (1 + \lambda_n V_{\rm DS}).$$

(3)

After substituting the equations for  $\alpha$  and  $g_m$  in (1), the current noise spectral density is

$$i_{n,d}^{\tilde{2}} = \frac{4kT\gamma}{\alpha} \cdot \left[ \mu_n C_{\text{ox}} \left( \frac{W}{L} \right) (V_{\text{GS}} - V_{\text{TH}}) (1 + \lambda_n V_{\text{DS}}) \right].$$

(4)

It can be observed from (4) that the thermal current noise spectral density of an MOS transistor depends on its mobility, physical dimensions, bias voltages, threshold voltage, oxide capacitance, and coefficients  $\alpha$ ,  $\gamma$ , and  $\lambda$ . As shown in Fig. 4(b), the dc bias voltages ( $V_{GS}$ ,  $V_{DS}$ ) are kept constants for all the selected cross-coupled pairs in the array used to implement the proposed VCO. However, the other parameters in (4), such as mobility, effective channel length, threshold voltage, and gate dielectric layer thickness, can significantly vary [27]–[29], which leads to the thermal noise variation. This implies that, if only the transistors with lower thermal noise can be used by post-fabrication selection, then it should also be possible to reduce the thermal noise impact on the overall PN.

# IV. VCO USING AN ARRAY OF NEAR MINIMUM-SIZED TRANSISTORS

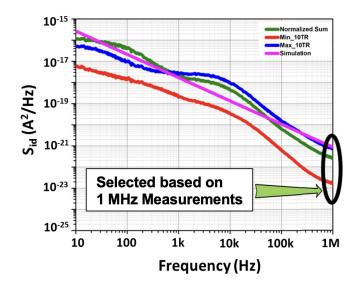

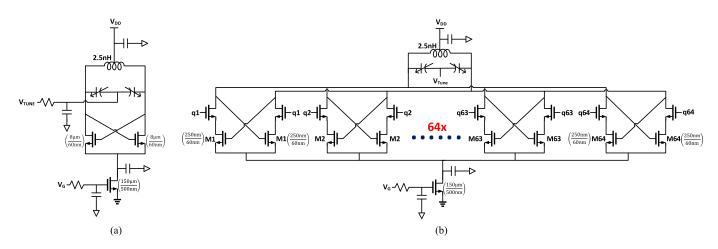

To demonstrate the technique of reducing the impact of low-frequency noise and thermal noise in an LC VCO by using an array of transistors sized near the minimum and post-fabrication selection, a VCO operating around 4 GHz [30] using an array of cross-coupled pairs of near minimumsize transistors is implemented. To start, a conventional VCO using a cross-coupled nMOS pair of 8  $\mu$ m width and 60 nm length with an nMOS tail current source, as shown in Fig. 4(a), is first designed. By using a long and wide nMOS tail current transistor of 150  $\mu$ m width and 500 nm length, the noise of the cross-coupled devices is made the dominant source. A high-Q 8-pF bypass capacitor at the drain node of the current source effectively prevents the injection of the thermal noise of current source transistor to the oscillator core [42].

The top plate of varactors is connected to  $V_{DD}$  through the tank inductor. The 2.5-nH tank inductor is formed with a five-turn circular symmetric center-tapped structure. It has a simulated Q-factor of 12 at 4 GHz. The varactors are of an accumulation mode type implemented as an nMOS structure in an *n*-well [43]. Fig. 4(b) shows the proposed VCO that uses an addressable array of 16 × 4 (64) nMOS crosscoupled transistor pairs for post-fabrication selection of pairs with reduced low-frequency and thermal noise. Each transistor forming the cross-coupled pair in Fig. 4(a) is divided into 32 transistors of a width and a length of 250 and 60 nm, respectively, or an area of 15 000 nm<sup>2</sup>. To provide redundancy, 32 additional pairs are added. Each unit also includes 2.5- $\mu$ m wide switches at the drains of the cross-coupling transistors for selection.

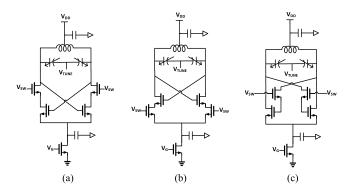

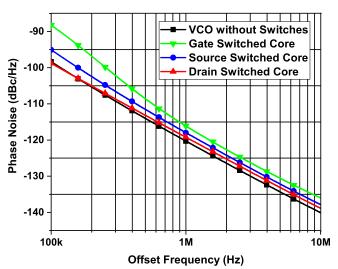

The selection switches for a pair can be placed at the gate, drain, or source of the transistors, as shown in Fig. 5. The PN with the switch at the gate of the transistor is worse than that for the VCO with the switch at the drain of the transistor for the same switch size. This is due to the switch resistance being in series with the gate impedance of the crosscoupled transistors. The thermal noise associated with the ON-resistance,  $R_{on}$  of switch has more impact for the gateswitched core compared to that of the drain-switched core. When referred to the output, the noise of the switch at the gate is amplified by the transistor gain, resulting in a higher noise contribution compared to that of the drain-switched core. The ON-resistance also lowers the output swing. The switch

Fig. 4. (a) Conventional nMOS VCO. (b) Proposed VCO using an array of cross-coupled near minimum-sized nMOS transistor pairs.

Fig. 5. (a) Drain-switched core. (b) Source-switched core. (c) Gate-switched core.

at the gate can be sized larger to reduce the gate resistance, but this, however, increases the parasitic capacitances of the switch and the cell area.

The source-switched core topology has a lower output swing than that of the drain-switched core due to the degeneration effect caused by the switch resistance at the source of core transistors. This, in turn, makes the PN of the source-switched core higher compared to that of the drain-switched core. Fig. 6 shows the simulated PN of a VCO using the array with different placements of switches at the tuning voltage of 0 V and with 32 cross-coupled transistor pairs switched ON. A switch with 2.5  $\mu$ m width and 60 nm length is used. The PN of VCO using the array with the drain switched core at a 1-MHz offset is -119 dBc/Hz from a 3.83-GHz carrier, whereas the PN of the gate switched core is -116 dBc/Hz at a 1-MHz offset, which is 3 dB higher than that of the drain switched core. The PN of the source switched core is -118 dBc/Hz at a 1-MHz offset, which is 1 dB higher than that of the drain switched core.

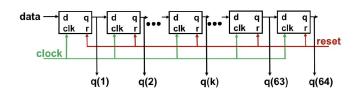

The switches for the 64 pairs of cross-coupled transistors are controlled by a 64-bit serial-in-parallel-out (SIPO) D flipflop chain. The D flip-flop is falling edge-triggered. A block diagram of the 64-bit SIPO is shown in Fig. 7. The switch size, as mentioned earlier, is chosen to ensure the additional parasitics of the switches do not significantly degrade both the

Fig. 6. Simulated PN of VCO with and without switches for post-fabrication selection.

Fig. 7. Block diagram of the 64-bit SIPO chain of D flip-flops.

PN performance and tuning range of the VCO using the array compared to that of the conventional VCO. Fig. 6 also shows the simulated PN of the conventional VCO at a tuning voltage of 0 V. Compared to the VCO without switches, there is  $\sim$ 1-dB PN degradation for the VCO using the array with drain-side switching. The PN of the conventional VCO is -120 dBc/Hz at a 1-MHz offset from a 3.98-GHz carrier.

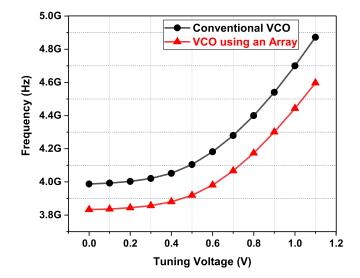

Fig. 8 shows the tuning range comparison between the conventional VCO without switches and VCO using the array with drain side switching and 32 cross-coupled pairs switched ON. The conventional VCO without switches oscillates from

Fig. 8. Tuning ranges of the Conventional VCO without switches and VCO using an array with drain side switching.

Fig. 9. Flowchart of the genetic algorithm.

3.98 to 4.87 GHz, which corresponds to a simulated tuning range of 20%. The VCO using the array with drain side switching achieves a simulated tuning range of 18% from 3.83 to 4.59 GHz, which is only 2% smaller compared to the tuning range of conventional VCO.

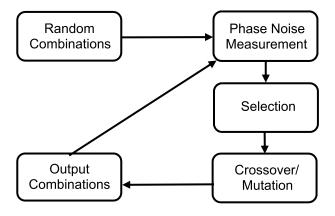

### V. INTELLIGENT SEARCH VIA GENETIC ALGORITHM

Searching among the vast space of 2<sup>64</sup> possible combinations of switched-ON cross-coupled transistor pairs to identify the ones having a given PN target requires an intelligent algorithm. A Hamming distance-driven search [30] explores a predetermined number of options in the Hamming distance vicinity of an initial seed and may converge to a local minimum. Instead, a classic genetic algorithm, which introduces more entropy in the search and is particularly efficient in exploring high-dimensional unstructured spaces, is employed. In addition, the genetic algorithm makes no assumptions about the search space and is driven by randomness, which makes it superior in searching for the combinations having low PN in a large space. A flowchart of the genetic algorithm is shown in Fig. 9. It defines the PN at a particular offset frequency as a "fitness function" to be optimized.

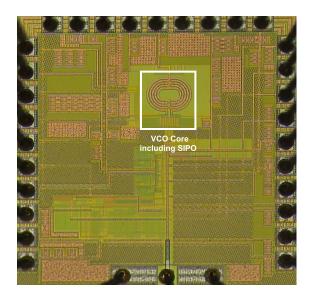

Fig. 10. Die micrograph.

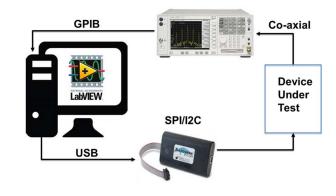

Fig. 11. Measurement setup for PN.

Each cross-coupled transistor pair is represented by a bit, with a value of "1" indicating that the pair is switched ON. The algorithm starts by generating a random population of chromosomes (i.e., binary strings with a varying length) with a user-defined range of the number of "1"s for which the fitness function is measured. The top 50% of the initial population with the lowest PN is retained, and the rest of the population is discarded. The binary strings in the top 50% of the population are named "parent strings."

The population is then replenished with new chromosomes by mutating the pairs of parent strings at a randomly chosen bit-location, called a "crossover point". All the bits to the right of the crossover point are swapped between the pairs of parent strings to generate new offspring strings. The rationale of this operation is that, after multiple generations, the mutation will allow a sufficiently diverse space to be explored, while the crossover will discard the bits having high PN in the parent strings, thereby generating new offspring strings with lower PN. The algorithm continues until a fitness limit specified by a user is achieved or until a sufficient number of combinations with adequately low PN are found.

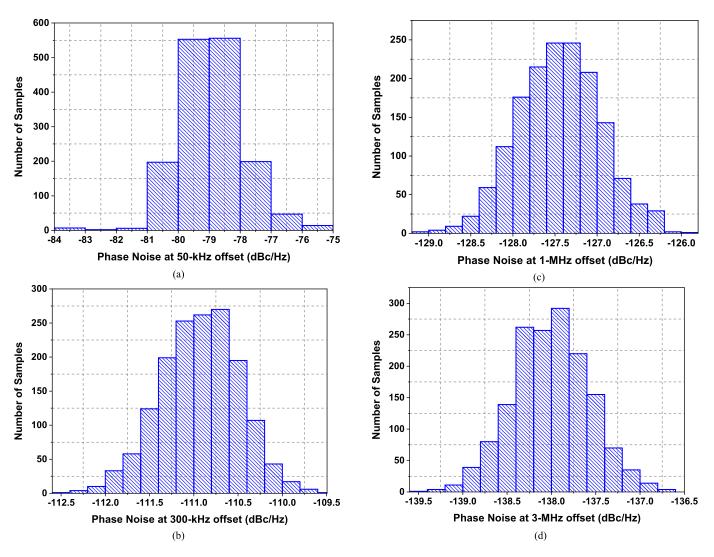

Fig. 12. Histograms of PN at (a) 50-kHz offset, (b) 300-kHz offset, (c) 1-MHz offset, and (d) 3-MHz offset from a 3.8-GHz carrier when 32 cross-coupled transistor pairs are switched ON.

# VI. MEASUREMENT RESULTS

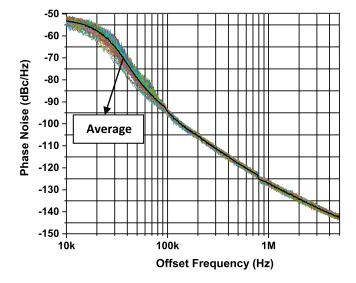

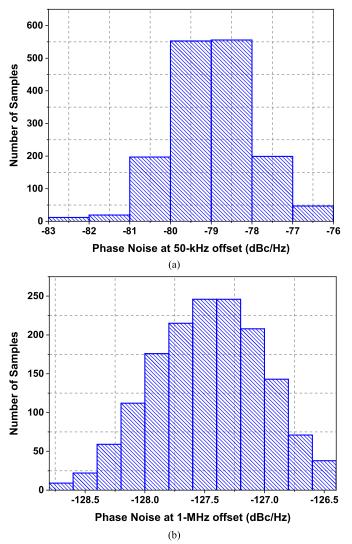

A prototype of the proposed VCO was fabricated in a 65-nm CMOS process with ten copper layers and one aluminum bond pad layer, and wire-bonded onto a printed circuit board (PCB) for measurements. The die micrograph is shown in Fig. 10. The core area of the VCO, including SIPO, is 0.025 mm<sup>2</sup>. A setup for measuring the PN with different combinations of cross-coupled pair units is shown in Fig. 11. 32 of the 64 cross-coupling transistor pairs are switched ON in the VCO by sending a random set of 32 "1" bits using LabVIEW to the DUT using an SPI/I2C interface. PN is measured using the PLL method of the Keysight E5052B Signal Source Analyzer with an average of 50 and is collected using LabVIEW. Fig. 12 shows the histograms of measured PN variations of ~1500 combinations at 50-kHz, 300-kHz, 1-MHz, and 3-MHz offsets from a 3.8-GHz carrier, respectively, when 32 cross-coupled transistor pairs out of the 64 pairs are switched ON. Fig. 13 shows the PN plots of these 1500 combinations.

Two main observations can be made from these figures: 1) from 10-kHz offset to 60-kHz offset, PN variation is around

9 dB, which mainly is due to the low-frequency noise variation of the core devices being the dominant determining factor and 2) PN variation is  $\sim$ 3.5 dB at higher offsets of 1 and 3 MHz, respectively. The PN variation decreases with an increasing offset because the contributions of thermal noise increase at higher frequency offsets.

It can also be noted from Fig. 13 that the lowest PN is 9 dB lower than the maximum PN at a 50-kHz offset, whereas it is  $\sim$ 3–3.5 dB lower than the maximum PN at 1- and 3-MHz offsets. Fig. 14 shows the histograms of PN variations of  $\sim$ 1500 random combinations at 50-kHz and 1-MHz offsets from a 3.78-GHz carrier when 48 cross-coupling transistor pairs out of the 64 pairs are switched ON. The PN variations are  $\sim$ 7 dB at a 50-kHz offset and  $\sim$ 2.5 dB at a 1-MHz offset. These variations are 2 and 1 dB lower than that when 32 pairs are selected out of 64, respectively.

The reduction of PN variation with an increasing number of switched-ON cross-coupling pairs can be attributed mainly to the law of large numbers. In addition to the variations in lowfrequency noise and the thermal noise, variations in the carrier

Fig. 13. Measured PN plots when 32 cross-coupled transistor pairs are switched ON. Average PN is also shown in the figure.

power of cross-coupling transistor pairs can also contribute to the PN variation. The variation of the output power for the combinations with an equal number of cross-coupled pairs switched ON should be mainly due to the variations in the VCO bias current and parallel resistance  $R_p$  of the tank due to the variations of the output resistance of the cross-coupling transistor pairs.

The output power ( $P_o$ ) in an LC VCO is directly proportional to the square of the product of the current flowing through the cross-coupled pairs ( $I_{cp}$ ) and the total parallel resistance ( $R_p$ ) in the tank [40], as given in the following equation:

$$P_o \propto \left( I_{\rm cp} R_p \right)^2. \tag{5}$$

Since  $I_{cp}$  is set by the current source, the power variation should be mostly due to the variation of  $R_p$ . Neglecting the losses due to the gate resistance, substrate resistance, and varactor,  $R_p$ , as shown in (6), can be given by the parallel combination of the equivalent resistance ( $R_{pL}$ ) of inductor and output resistance ( $R_{ds}$ ) of the transistors in the cross-coupled pairs [44]

$$R_p = R_{pL} \| R_{\rm ds}. \tag{6}$$

The total  $R_{ds}$  in the VCO array is given by the following equation:

$$R_{\rm ds} = R_{\rm ds,1} \| R_{\rm ds,2} \| R_{\rm ds,3}, \dots, R_{\rm ds,n}$$

(7)

where  $R_{ds,1}-R_{ds,n}$  are the output resistances of a single transistor from each selected cross-coupled transistor pair, and *n* is the total number of pairs switched ON out of 64.

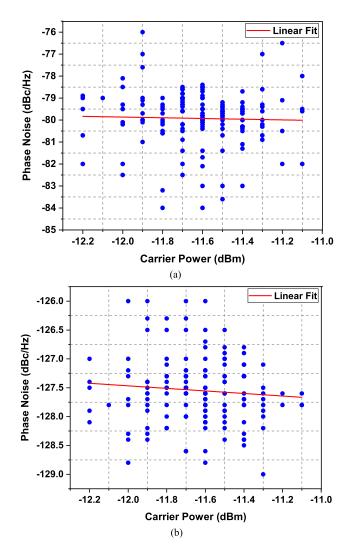

Fig. 15(a) and (b) shows the correlation between the carrier power and PN at 50-kHz and 1-MHz offsets, respectively, when 32 cross-coupled transistor pairs are switched ON. Randomly chosen subsets of combinations from PN bins in Fig. 13 are selected for carrier power measurements. The variation in carrier power is only  $\sim$ 1 dB for 32 selected pairs. A maximum PN variation of  $\sim$ 6 dB is observed at a carrier power of -11.6 dBm at a 50-kHz offset, and the correlation

Fig. 14. Histograms of PN at (a) 50-kHz offset and (b) 1-MHz offset from a 3.78-GHz carrier when 48 cross-coupled pairs are switched ON.

coefficient using the linear fit shown in Fig. 15(a) is only 3%, whereas, at a 1-MHz offset, a maximum PN variation of  $\sim$ 3 dB is observed at multiple carrier power levels (-11.6, -11.7, and -12 dBm), and the correlation coefficient using the linear fit shown in Fig. 15(b) is only 9%. These results indicate that the variation of PN is not due to the carrier power variation.

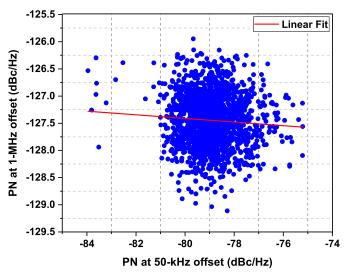

Fig. 16 shows the PN at 1 MHz versus that at 50 kHz for the samples used for the histograms in Fig. 13. The PN at a 50-kHz offset limited by the low-frequency noise is not correlated with the PN at a 1-MHz offset where the thermal noise contribution dominates. The correlation coefficient using the linear fit shown in the figure is only 7%. The correlation of low-frequency noise to thermal noise due to correlated increased mobility due to lower trap density [45] is not observed. The genetic algorithm for post-fabrication selection is coded in Python and integrated with LabVIEW. Offset frequencies of 50 kHz, 1 MHz, and 3 MHz were used in the genetic algorithm to lower the PN. Around 100 combinations were generated by the algorithm in each generation. The user-defined range for the number of selected cross-coupling pairs is between 20 and 60.

Fig. 15. PN versus Carrier Power at (a) 50-kHz offset and (b) 1-MHz offset from the 3.8-GHz carrier when 32 cross-coupled pairs are switched ON.

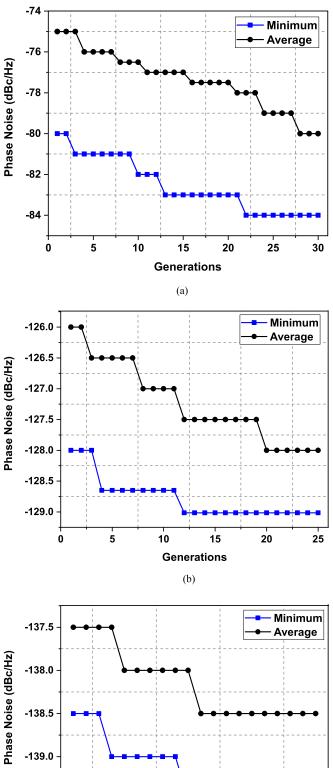

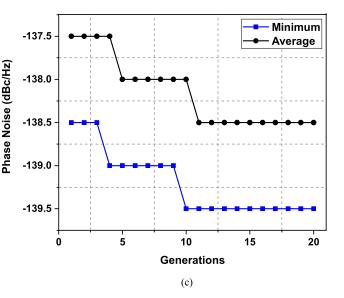

Fig. 17 shows the measured lowest PN at 50-kHz, 1-MHz, and 3-MHz offsets, respectively, at varying generations. The genetic algorithm converges to the combinations having the lowest PN of -84 dBc/Hz at a 50-kHz offset, -129 dBc/Hz at a 1-MHz offset, and -139.5 dBc/Hz at a 3-MHz offset, respectively, from a 3.8-GHz carrier. Fig. 18 shows the PN plot of the best combination having the lowest PN of -129 dBc/Hz at a 1-MHz offset from a 3.8-GHz carrier when 32 crosscoupling pairs are selected. The slope of -2 is also shown in the figure, which is between 900-kHz and 9-MHz offsets.

The lowest PN when 32 pairs are switched ON is 0.5 dB lower at a 1-MHz offset than that for the best combination when 48 pairs are selected, whereas the PN when all the 64 pairs are switched ON is -126.5 dBc/Hz at a 1-MHz offset, which is 2.5 dB higher than that for the best combination having 32 selected pairs. Raising the number of selected cells increases the overall transistor width while keeping the VCO dc current constant due to the tail current source. This increases the transconductance while keeping  $R_{ds}$ ; thus,  $R_P$  is approximately constant, thereby increasing the VCO loop gain  $(g_m R_p)^2$ . This indicates that the PN of VCO loop gain.

Fig. 16. PN at 1-MHz offset versus that at a 50-kHz offset when 32 crosscoupled transistor pairs are switched ON.

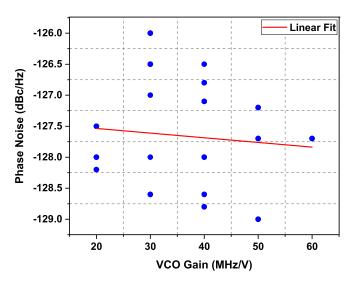

Variations of the VCO gain ( $K_{vco}$ ) among different combinations of selected cross-coupled pairs can also contribute to the PN variation since a higher VCO gain leads to higher PN due to increased AM–PM conversion and vice versa [46], [47]. Fig. 19 shows the PN at a 1-MHz offset versus measured VCO gain for the samples used for the histograms in Fig. 12. 32 cross-coupled transistor pairs were switched ON. The VCO gain shown in the figure is measured for a tuning voltage at 0.05 V near which the measured PN is minimum. As observed in Fig. 19, the maximum PN variation of ~3 dB is observed at the VCO gains of 30 and 40 MHz/V. The correlation coefficient using a linear fit shown in Fig. 20 is only 10%. This shows that the PN variations of the VCO using the array are not due to variations of the VCO gain.

This process of elimination and the fact that PN can vary by many dBs at a given VCO output power and gain suggest that the likely cause for the PN variation is the variations of the low-frequency noise and the thermal noise. The increase in PN by 2.5 dB when all the 64 pairs are switched ON compared to the case when 32 pairs are selected shows that there exists some pairs of transistors having high thermal noise and low-frequency noise, and these pairs should be discarded to reduce the PN. The VCO was characterized using the PLL method in E5052B because multiple works reporting low PN VCO have used the PLL method of E5052B for their measurements [16], [20].

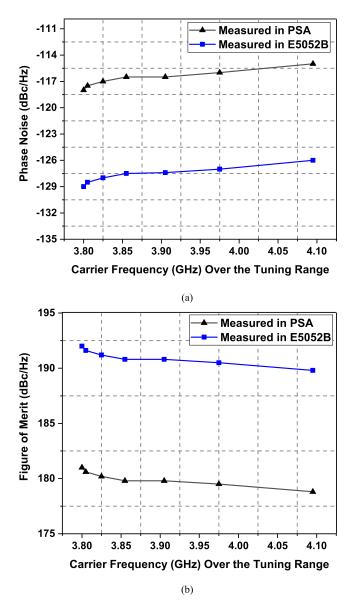

The VCO in this work was also characterized using the PN utility in Keysight E4440A PSA. The lowest PN measured using the E4440A PSA is 11 dB higher than that in E5052B. Improvements are expected from using the PLL method in E5052B because it locks the free-running VCO to measure its PN. The 11-dB difference seems large. Measurements were checked and repeated multiple times to ensure the proper operation of the instruments. Because of this, the figure of merit (FoM) in (8) normalizing the oscillation frequency ( $f_o$ ), power dissipation ( $P_{dc}$ ), and PN ( $L_{offset}$ ) at a particular offset frequency ( $f_{offset}$ ) have been estimated from the measurements

-50

-60

-70

-80 -90

Phase Noise (dBc/Hz) -100 -110 -120 -130 -140 -150 Slope = -2 -160 100k 1M 10k 10M **Offset Frequency (Hz)**

Fig. 18. PN of the best combination having the lowest PN at a 1-MHz offset from a 3.8-GHz carrier.

Fig. 17. PN reduction using the Genetic algorithm at (a) 50-kHz offset, (b) 1-MHz offset, and (c) 3-MHz offsets from a 3.8-GHz carrier.

Fig. 19. PN at 1-MHz offset versus VCO gain when 32 cross-coupled pairs are switched ON.

from both E4440A PSA and E5052B

$$FoM = 20 \log\left(\frac{f_0}{f_{offset}}\right) - L_{offset} - 10 \log\left(\frac{P_{dc}}{1 \text{ mW}}\right).$$

(8)

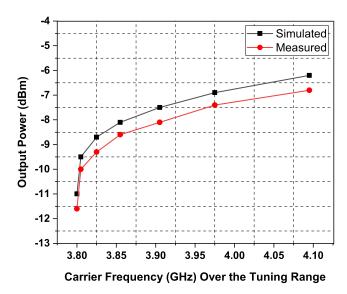

Fig. 20(a) and (b) shows the PN and FoM at a 1-MHz offset across the measured tuning range of 3.8-4.1 GHz for the best combination, respectively. There is  $\sim$ 3-dB variation of PN at a 1-MHz offset across the tuning range. The peak FoM of 192 dBc/Hz at a 1-MHz offset is achieved at the minimum frequency of 3.8 GHz where the tuning voltage is 0 V. The FoM measured in the PSA is 11 dB lower than that in E5052B. There is  $\sim$ 2-dB variation of FoM across the tuning range. This is due to the PN degradation at higher tuning voltages, which, in turn, is caused by the higher AM-PM conversion due to higher VCO gains [46], [47]. This problem can be resolved by linearizing the VCO tuning curve with a programmable capacitor bank and, thereby, maintaining a lower  $K_{vco}$  over the entire tuning range [48]. Nevertheless, the VCO still achieves

Fig. 20. (a) PN at 1-MHz offset and (b) FoM at 1-MHz offset for the best combination across the tuning range.

an FoM of greater than 189.5 dBc/Hz (measured in E5052B) over the tuning range. Fig. 21 shows the output power across the tuning range. Compared to the simulated output power, there is only 0.5-dB degradation in the measured output power across the tuning range for the best combination.

Table I summarizes the improvements of PN from the average and maximum PNs at various offsets from the 3.8-GHz carrier. The PN at a 50-kHz offset is lowered by 5–6 dB from the average PN in the measurements done in both PSA and E5052B, and by 9 dB from the maximum in E5052B and by 12 dB in PSA, whereas at 600-kHz, 1-MHz, and 3-MHz offsets, it is lowered by 1.5–2 dB from the average and  $\sim$ 3.5 dB from the maximum. Both the measurements using the PSA and E5052B show that PN can be lowered by applying an intelligent post-fabrication selection process to a VCO employing an array of individually selectable cross-coupled pairs of transistors with dimensions near the minimum for a given process.

Fig. 21. Output Power across the tuning range for the best combination.

TABLE I PN Improvement From Average and Maximum at Various Offset Frequencies

| Offset  | Improvement | Improvement | Improvement | Improvement |  |

|---------|-------------|-------------|-------------|-------------|--|

|         | from        | from Max    | from        | from Max    |  |

|         | Average     | (in E5052B) | Average     | (in PSA)    |  |

|         | (in E5052B) |             | (in PSA)    |             |  |

| 50 kHz  | 5 dB        | 9 dB        | 6 dB        | 12 dB       |  |

| 600 kHz | 2 dB        | 3.5 dB      | 2 dB        | 3.5 dB      |  |

| 1 MHz   | 2 dB        | 3.5 dB      | 2 dB        | 3.5 dB      |  |

| 3 MHz   | 1.5 dB      | 3 dB        | 1.5 dB      | 3.5 dB      |  |

Table II summarizes the performance and benchmarks the proposed VCO using an array of cross-coupled pairs in this article with that of the other low PN CMOS LC VCOs in the literature. The main aim of this article is to verify the proposed technique. The peak FoM of the VCO array is 193 dBc/Hz at a 3-MHz offset from a 3.8-GHz carrier. Another FoM, FoM<sub>A</sub> that also takes the core area of VCO into account, is calculated for all the works and included in the table. The VCO in this article exhibits an excellent FoM<sub>A</sub> of 209 dBc/Hz when the PN is measured using the PLL method in E5052B. Even from the PSA measurements, FoM<sub>A</sub> of 198 dBc/Hz is on par with the recently published low PN CMOS LC VCOs.

An important point to note is that the proposed technique for reducing PN using post-fabrication selection of transistor pairs sized near the minimum should be orthogonal to the other PN reduction techniques in the literature since the proposed method reduces the device noise itself. For instance, it can be used along with the harmonic shaping technique in a Class-F VCO and achieve an ultralow PN. A Class-F VCO creates a pseudosquare oscillation voltage in order to reduce its impulse sensitivity function, thus lowering the conversion sensitivity of various noise sources to the PN [17]. This along with the reduced device noise resulting from the technique proposed in this article should lead to lower PN. Finally, it should be possible to integrate an on-chip PN measurement circuit in order to make this technique more practical [49]–[54].

| TABLE II                                                     |

|--------------------------------------------------------------|

| Performance Benchmark With the State-of-the-Art CMOS LC VCOs |

|                                        | VCO<br>Topology                            | Frequency<br>(GHz) | PN at 1-MHz<br>offset<br>(dBc/Hz) | Power<br>Dissipation<br>(mW) | Tuning<br>Range<br>(%) | PN at 1-MHz<br>offset<br>(dBc/Hz)<br>Normalized<br>to 5 GHz | Peak FoM<br>(dBc/Hz) | Core area (mm <sup>2</sup> ) | <sup>1</sup> Peak FoM <sub>A</sub><br>(dBc/Hz) | CMOS<br>Technology |

|----------------------------------------|--------------------------------------------|--------------------|-----------------------------------|------------------------------|------------------------|-------------------------------------------------------------|----------------------|------------------------------|------------------------------------------------|--------------------|

| This Work<br>(PLL Method<br>in E5052B) | Class-B<br>NMOS<br>VCO using               | 3.8                | -129                              | 7                            | 7.8                    | -126.6                                                      | 193                  | 0.025                        | 209                                            | 65nm               |

| This Work<br>(E4440A PSA)              | Post-Fabrication<br>Selection              | 3.8                | -118                              | 7                            | 7.8                    | -115.6                                                      | 182                  | 0.025                        | 198                                            |                    |

| [5]<br>ISSCC'21                        | Wideband<br>Harmonic<br>Shaping            | 5                  | -130*                             | 6.1                          | 23.9                   | -130                                                        | 196.2                | 0.24                         | 202.4                                          | 65nm               |

| [6]<br>ISSCC'21                        | Multi-Core<br>Harmonic<br>Shaping          | 3.09               | -138.9                            | 20.9                         | 26.6                   | -134.7                                                      | 195.1                | 0.36                         | 199.5                                          | 40nm               |

| [7]<br>TMTT'20                         | VCO using an<br>Inversion mode<br>Varactor | 4.14               | -109                              | 0.82                         | 40.3                   | -107.4                                                      | 185                  | 0.436                        | 188.6                                          | 40nm               |

| [8]<br>JSSC'18                         | Inverse<br>Class-F                         | 4                  | -124.3                            | 1.2                          | 25.5                   | -122.3                                                      | 195.5                | 0.14                         | 204                                            | 65nm               |

| [9]<br>VLSI'17                         | Pulse-Tail<br>Feedback                     | 4.55               | -123.4                            | 1.35                         | 5.5                    | -122.6                                                      | 195.3                | N/A                          | N/A                                            | 180nm              |

| [10]<br>JSSC'16                        | Class-F <sub>2,3</sub>                     | 5.4                | -126.7                            | 12                           | 25                     | -127.3                                                      | 190.5                | 0.13                         | 199.3                                          | 40nm               |

| [11]<br>ISSCC'16                       | 2f <sub>o</sub> Implicit<br>Resonance      | 4.83               | -119                              | 0.5                          | 13.8                   | -118.7                                                      | 195.7                | 0.18                         | 203.1                                          | 28nm               |

| [12]<br>JSSC'15                        | Class-F <sub>2</sub>                       | 4.35               | -135*                             | 41.6                         | 19                     | -133.8                                                      | 191.6                | 0.2                          | 198.6                                          | 65nm               |

| [13]<br>ISSCC'15                       | ISF<br>Manipulation                        | 2.4                | -128.4                            | 4.2                          | 1.7                    | -122                                                        | 189.8                | 0.09                         | 200.2                                          | 130nm              |

| [14]<br>RFIC'15                        | Harmonic<br>VCO                            | 5.8                | -117*                             | 8                            | 70                     | -118.3                                                      | 183.3                | 0.27                         | 189                                            | 28nm               |

| [15]<br>RFIC'15                        | Class-B<br>Mode Switching                  | 6.48               | -114*                             | 2.2                          | 74.6                   | -116.3                                                      | 186.8                | 0.126                        | 195.8                                          | 65nm               |

| [16]<br>ISSCC'14                       | Class-B<br>Mode Switching                  | 3.72               | -129.3                            | 20                           | 88.7                   | -126.7                                                      | 187.7                | 0.432                        | 191.3                                          | 40nm               |

| [17]<br>JSSC'13                        | Class-F                                    | 3.7                | -131                              | 15                           | 25                     | -128.4                                                      | 190.6                | 0.12                         | 199.8                                          | 65nm               |

| [18]<br>JSSC'13                        | Class-C                                    | 3.42               | -127*                             | 6.6                          | 28                     | -123.7                                                      | 189.5                | 0.08                         | 200.5                                          | 90nm               |

| [19]<br>TMTT'13                        | VCO using a<br>Segmented<br>Transconductor | 2.1                | -124                              | 8                            | 47.6                   | -116.5                                                      | 181.4                | 0.121                        | 190.6                                          | 65nm               |

| [20]<br>JSSC'12                        | Class-B<br>Mode Switching                  | 3.69               | -128.3                            | 10.4                         | 76.5                   | -125.6                                                      | 189.5                | 0.294                        | 194.8                                          | 65nm               |

| [21]<br>RFIC'11                        | VCO using a<br>5-Port Inductor             | 4.4                | -120                              | 7.1                          | 199                    | -118.9                                                      | 184.4                | 0.36                         | 188.8                                          | 180nm              |

\*Estimated from the phase noise plot  ${}^{1}\text{FOM}_{A} = 20\log\left(\frac{f_{0}}{f_{offset}}\right) - L_{offset} - 10\log\left(\frac{P_{DC}}{1mW}\right) - 10\log\left(\frac{Area}{1mm^{2}}\right)$

# VII. CONCLUSION

A technique for reducing the PN of LC VCOs by employing an array of individually selectable cross-coupled pairs formed using transistors with dimensions near the minimum and by employing an intelligent post-fabrication selection is demonstrated. This technique reduces the PN by taking advantage of the fact that, when transistor dimensions are reduced, the low-frequency noise and the thermal noise can vary significantly, and the low-frequency noise at the lower end of its distribution is decreased. Using minimum-sized transistors to reduce the impact of low-frequency noise is opposite to the conventional approach of using larger transistors, which relies on averaging the value determined by the PDK model. Applying an intelligent post-fabrication selection process using a genetic algorithm well suited for searching through high-dimensional unstructured spaces to an LC VCO employing the array, the PN at 600-kHz, 1-MHz, and 3-MHz offsets from a 3.8-GHz carrier is lowered by 1.5–2 dB from the average PN and by  $\sim$ 3.5 dB from the maximum PN. It should be possible to utilize the proposed technique with other PN reduction techniques to realize the ultralow PN oscillators. Finally, it may be possible to increase the operating frequencies of VCOs using the proposed technique, and the investigation of this is an important vector for future research.

#### ACKNOWLEDGMENT

The authors are grateful to Dr. S. Huang for the lowfrequency noise data of MOS transistors fabricated in 65-nm CMOS.

#### REFERENCES

- J. Cavazos. Overcoming 5G NR mmWave Signal Quality Challenges. Accessed: Sep. 30, 2019. [Online]. Available: https://blogs.keysight.com

- [2] H. Afzal, R. Abedi, R. Kananizadeh, P. Heydari, and O. Momeni, "An mm-wave scalable PLL-coupled array for phased-array applications in 65-nm CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 2, pp. 1439–1452, Feb. 2021, doi: 10.1109/TMTT.2020.3039517.

- [3] K. Kibaroglu, M. Sayginer, and G. M. Rebeiz, "A 28 GHz transceiver chip for 5G beamforming data links in SiGe BiCMOS," in *Proc. IEEE Bipolar/BiCMOS Circuits Technol. Meeting (BCTM)*, Oct. 2017, pp. 74–77, doi: 10.1109/BCTM.2017.8112914.

- [4] Y. Wang et al., "A 260-mW Ku-band FMCW transceiver for synthetic aperture radar sensor with 1.48-GHz bandwidth in 65-nm CMOS technology," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 11, pp. 4385–4399, Nov. 2017.

- [5] H. Guo, Y. Chen, P.-I. Mak, and R. P. Martins, "A 5.0-to-6.36 GHz wideband-harmonic-shaping VCO achieving 196.9 dBc/Hz peak FoM and 90-to-180 kHz 1/f<sup>3</sup> PN corner without harmonic tuning," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2021, pp. 294–296.

- [6] Y. Shu, H. J. Qian, X. Gao, and X. Luo, "A 3.09-to-4.04 GHz distributedboosting and harmonic-impedance-expanding multi-core oscillator with-138.9 dBc/Hz at 1 MHz offset and 195.1 dBc/Hz FoM," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2021, pp. 296–298.

- [7] M. Fang and T. Yoshimasu, "A –197.3-dBc/Hz FoM<sub>T</sub> wideband LC-VCO IC with a single voltage-controlled IMOS-based novel varactor in 40-nm CMOS SOI," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 10, pp. 4116–4121, Oct. 2020.

- [8] C. C. Lim, H. Ramiah, J. Yin, P.-I. Mak, and R. P. Martins, "An inverseclass-F CMOS oscillator with intrinsic-high-Q first harmonic and second harmonic resonances," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3528–3539, Dec. 2018.

- [9] A. T. Narayanan, N. Li, K. Okada, and A. Matsuzawa, "A pulse-tail-feedback VCO achieving FoM of 195 dBc/Hz with flicker noise corner of 700 Hz," in *Proc. Symp. VLSI Circuits*, Jun. 2017, pp. C124–C125.

- [10] M. Shahmohammadi, M. Babaie, and R. B. Staszewski, "A 1/f noise upconversion reduction technique for voltage-biased RF CMOS oscillators," *IEEE J. Solid-State Circuits*, vol. 51, no. 11, pp. 2610–2624, Nov. 2016.

- [11] D. Murphy and H. Darabi, "A complementary VCO for IoE that achieves a 195 dBc/Hz FOM and flicker noise corner of 200 kHz," in *IEEE ISSCC Dig. Tech. Papers*, Jan. 2016, pp. 44–45.

- [12] M. Babaie and R. B. Staszewski, "An ultra-low phase noise class-F<sub>2</sub> CMOS oscillator with 191 dBc/Hz FoM and long-term reliability," *IEEE J. Solid-State Circuits*, vol. 50, no. 3, pp. 679–692, Mar. 2015.

- [13] A. Mostajeran, M. S. Bakhtiar, and E. Afshari, "A 2.4 GHz VCO with FOM of 190 dBc/Hz at 10 kHz-to-2 MHz offset frequencies in 0.13μm CMOS using an ISF manipulation technique," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2015, pp. 452–453.

- [14] L. Fanori, A. Mahmoud, T. Mattsson, P. Caputa, S. Ramo, and P. Andreani, "A 2.8-to-5.8 GHz harmonic VCO in a 28 nm UTBB FD-SOI CMOS process," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2015, pp. 195–198.

- [15] A. Agrawal and A. Natarajan, "A 6.39 GHz–14 GHz series resonator mode-switching oscillator with 186–188 dB FoM and 197 dB FoMA in 65 nm CMOS," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.* (*RFIC*), May 2015, pp. 199–202.

- [16] M. Taghivand, K. Aggarwal, and A. S. Y. Poon, "A 3.24-to-8.45 GHz low-phase-noise mode-switching oscillator," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2014, pp. 368–369.

- [17] M. Babaie and R. B. Staszewski, "A class-F CMOS oscillator," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3120–3133, Dec. 2013.

- [18] L. Fanori and P. Andreani, "Highly efficient class-C CMOS VCOs, including a comparison with class-B VCOs," *IEEE J. Solid-State Circuits*, vol. 48, no. 7, pp. 1730–1740, Jul. 2013.

- [19] F. Pepe, A. Bonfanti, S. Levantino, C. Samori, and A. L. Lacaita, "Analysis and minimization of flicker noise up-conversion in voltagebiased oscillators," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 6, pp. 2382–2394, Jun. 2013.

- [20] G. Li, L. Liu, Y. Tang, and E. Afshari, "A low-phase-noise wide-tuningrange oscillator based on resonant mode switching," *IEEE J. Solid-State Circuits*, vol. 47, no. 6, pp. 1295–1308, Jun. 2012.

- [21] W. Deng, K. Okada, and A. Matsuzawa, "A 25 MHz–6.44 GHz LC-VCO using a 5-port inductor for multi-band frequency generation," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2011, pp. 1–4.

- [22] E. G. Ioannidis *et al.*, "Low frequency noise variability in high-k/metal gate stack 28 nm bulk and FD-SOI CMOS transistors," in *IEDM Tech. Dig.*, Dec. 2011, pp. 449–452.

- [23] E. Simoen, A. Veloso, Y. Higuchi, N. Horiguchi, and C. Claeys, "On the oxide trap density and profiles of 1-nm EOT metal-gate last CMOS transistors assessed by low-frequency noise," *IEEE Trans. Electron Devices*, vol. 60, no. 11, pp. 3849–3855, Nov. 2013.

- [24] G. I. Wirth, J. Koh, R. da Silva, R. Thewes, and R. Brederlow, "Modeling of statistical low-frequency noise of deep-submicrometer MOSFETs," *IEEE Trans. Electron Devices*, vol. 52, no. 7, pp. 1576–1588, Jul. 2005.

- [25] D. Lopez, S. Haendler, C. Leyris, G. Bidal, and G. Ghibaudo, "Low frequency noise investigation and noise variability analysis in high-k/metal gate 32-nm CMOS transistors," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2310–2316, Aug. 2011.

- [26] M. Erturk, T. Xia, R. L. Wolf, D. P. Scagnelli, and W. F. Clark, "Statistical variations in VCO phase noise due to upconverted MOSFET 1/f noise," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2008, pp. 255–258.

- [27] K. Bernstein *et al.*, "High-performance CMOS variability in the 65-nm regime and beyond," *IBM J. Res. Develop.*, vol. 50, no. 4, pp. 433–449, Jul. 2006.

- [28] W. Zhao et al., "Rigorous extraction of process variations for 65-nm CMOS design," *IEEE Trans. Semicond. Manuf.*, vol. 22, no. 1, pp. 196–203, Feb. 2009.

- [29] S. Saxena *et al.*, "Variation in transistor performance and leakage in nanometer-scale technologies," *IEEE Trans. Electron Devices*, vol. 55, no. 1, pp. 131–144, Jan. 2008.

- [30] A. Jha et al., "-197 dBc/Hz FOM 4.3-GHz VCO using an addressable array of minimum-sized NMOS cross-coupled transistor pairs in 65-nm CMOS," in Proc. IEEE Symp. VLSI Circuits (VLSI-Circuits), Jun. 2016, pp. 1–2.

- [31] M. P. Flynn, C. Donovan, and L. Sattler, "Digital calibration incorporating redundancy of flash ADCs," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 50, no. 5, pp. 205–213, May 2003.

- [32] J. Proesel, G. Keskin, J.-O. Plouchart, and L. Pileggi, "An 8-bit 1.5 GS/s flash ADC using post-manufacturing statistical selection," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Sep. 2010, pp. 1–4.

- [33] A. L. McWorther, "1/f noise and related surface effects in germanium," Ph.D. dissertation, MIT, Cambridge, MA, USA, 1955.

- [34] R Van Langevelde, A. J. Scholten, and D. B. M. Klaassen, "Physical background of MOS model 11," Koninklijke Philips Electron. N.V., Tech. Rep. NL-TN 2004/00085, Apr. 2003.

- [35] M.-H. Tsai and T.-P. Ma, "The impact of device scaling on the current fluctuations in MOSFETs," *IEEE Trans. Electron Devices*, vol. 41, no. 11, pp. 2061–2068, Nov. 1994.

- [36] G. Reimbold, "Modified 1/f trapping noise theory and experiments in MOS transistors biased from weak to strong inversion—Influence of interface states," *IEEE Trans. Electron Devices*, vol. ED-31, no. 9, pp. 1190–1198, Sep. 1984.

- [37] G. Ghibaudo, O. Roux-Dit-Buisson, and J. Brini, "Impact of scaling down on low frequency noise in silicon MOS transistors," *Phys. Status Solidi A*, vol. 132, no. 2, pp. 501–507, 1992.

- [38] K. K. Hung, P. K. Ko, C. Hu, and Y. C. Cheng, "A unified model for the flicker noise in metal-oxide-semiconductor field-effect transistors," *IEEE Trans. Electron Devices*, vol. 37, no. 3, pp. 654–665, Mar. 1990.

- [39] B. Boukriss, H. Haddara, S. Cristoloveanu, and A. Chovet, "Modeling of the 1/f noise overshoot in short-channel MOSFETs locally degraded by hot-carrier injection," *IEEE Electron Device Lett.*, vol. 10, no. 10, pp. 433–436, Oct. 1989.

- [40] B. Razavi, RF Microelectronics, 2nd ed. Prentice-Hall, 2012.

- [41] D. K. Shaeffer and T. H. Lee, "A 1.5-V, 1.5-GHz CMOS low noise amplifier," *IEEE J. Solid-State Circuits*, vol. 32, no. 5, pp. 745–759, May 1997.

- [42] C.-M. Hung, I.-C. Wu, and Y.-C. Ho, "High Q capacitors (>150 @ 900 MHz) implemented in a CMOS process for wireless applications," *IEEE Trans. Microw. Theory Techn.*, vol. 46, no. 5, pp. 505–511, May 1998.

- [43] C. M. Hung, B. A. Floyd, N. Park, and K. O. Kenneth, "Fully integrated 5.35-GHz CMOS VCOs and prescalers," *IEEE Trans. Microw. Theory Techn.*, vol. 49, no. 1, pp. 17–22, Jan. 2001.

- [44] S.-M. Yim, "Switched resonators and their applications in a dual-band monolithic CMOS LC-tuned VCO," *IEEE Trans. Microw. Theory Techn.*, vol. 54, no. 1, pp. 74–81, Jan. 2006.

- [45] R. Jayaraman and C. G. Sodini, "A 1/f noise technique to extract the oxide trap density near the conduction band edge of silicon," *IEEE Trans. Electron Devices*, vol. 36, no. 9, pp. 1773–1782, Sep. 1989.

- [46] S. Levantino, C. Samori, A. Zanchi, and A. L. Lacaita, "AM-to-PM conversion in varactor-tuned oscillators," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 49, no. 7, pp. 509–513, Jul. 2002.

- [47] E. Hegazi and A. A. Abidi, "Varactor characteristics, oscillator tuning curves, and AM–FM conversion," *IEEE J. Solid-State Circuits*, vol. 38, no. 6, pp. 1033–1039, Jun. 2003.

- [48] Z. Li, "A low-phase-noise and low-power multiband CMOS voltagecontrolled oscillator," *IEEE J. Solid-State Circuits*, vol. 40, no. 6, pp. 1296–1302, Jun. 2005.

- [49] K. Subburaj, S. Samala, and R. Ganesan, "Dynamic measurements of frequency synthesizer noise spurs on phase noise," U.S. Patent 2016/0191232, Jun. 30, 2016.

- [50] W. Khalil, B. Bakkaloglu, and S. Kiaei, "A self-calibrated on-chip phase-noise measurement circuit with -75 dBc single-tone sensitivity at 100 kHz offset," *IEEE J. Solid-State Circuits*, vol. 42, no. 12, pp. 2758–2765, Dec. 2007.

- [51] S. Min, T. Copani, S. Kiaei, and B. Bakkaloglu, "A 90-nm CMOS 5-GHz ring-oscillator PLL with delay-discriminator-based active phasenoise cancellation," *IEEE J. Solid-State Circuits*, vol. 48, no. 5, pp. 1151–1160, May 2013.

- [52] A. Melzer, A. Onic, and M. Huemer, "Online phase-noise estimation in FMCW radar transceivers using an artificial on-chip target," *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 12, pp. 4789–4800, Dec. 2016.

- [53] S. Hao, T. Hu, and Q. J. Gu, "A 10-GHz delay line frequency discriminator and PD/CP-based CMOS phase noise measurement circuit," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 7, pp. 2361–2372, Jul. 2017.

- [54] S. Hao *et al.*, "A CMOS phase noise filter with passive delay line and PD/CP-based frequency discriminator," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 11, pp. 4154–4164, Nov. 2017.

- [55] A. Jha et al., "Approaches to area efficient high-performance voltagecontrolled oscillators in nanoscale CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 1, pp. 147–156, Jan. 2021.

- [56] E. Hegazi, H. Sjoland, and A. A. Abidi, "A filtering technique to lower LC oscillator phase noise," *IEEE J. Solid-State Circuits*, vol. 36, no. 12, pp. 1921–1930, Dec. 2001.

- [57] H. Kim, S. Ryu, Y. Chung, J. Choi, and B. Kim, "A low phase-noise CMOS VCO with harmonic tuned LC tank," *IEEE Trans. Microw. Theory Techn.*, vol. 54, no. 7, pp. 2917–2924, Jul. 2006.

- [58] A. Hajimiri and T. H. Lee, "Design issues in CMOS differential LC oscillators," *IEEE J. Solid-State Circuits*, vol. 34, no. 5, pp. 716–724, May 1999.

**Pavan Yelleswarapu** (Member, IEEE) received the B.Tech. degree in electronics and communication engineering from the Gandhi Institute of Technology and Management (GITAM) University, Visakhapatnam, India, in 2013, and the M.S. and Ph.D. degrees in electrical engineering from The University of Texas at Dallas, Richardson, TX, USA, in 2015 and 2021, respectively.

He is currently a Senior RFIC/mmWave IC Design Engineer with Qualcomm Technologies, Inc., Richardson, where he is working on integrated cir-

cuits design for next-generation wireless communication systems. His research interests include integrated circuits and systems design for RF, millimeter-, and submillimeter-wave applications.

Amit Jha (Senior Member, IEEE) received the B.S. degree from IIT Madras, Chennai, India, in 2004, the M.S. degree from Penn State University, PA, USA, in 2007, and the Ph.D. degree from The University of Texas at Dallas, Richardson, TX, USA, in 2016.

He is currently a Staff RFIC Design Engineer with Qualcomm, San Jose, CA, USA, where he is working on RF circuits for next-generation wireless communications. His past experiences include the development of mmWave/high-speed circuits for

optical communications, RF front ends, and transistor compact models. Dr. Jha is also a Technical Program Committee Member of the Signal Generation Circuits Track at IEEE IMS and the RF, Millimeter-wave and THz Integrated Circuit Front Ends Track at IEEE RWW. He was a recipient of the Best Poster Award for "VCO Area Reduction in Nano-Scale CMOS Processes" at the SRC-TxACE ICSS Circuits Review in 2014. He is also the Co-Track Chair of the Non-Linear Circuits and Systems Subcommittee at IEEE ISCAS, Austin, 2022.

**Richard Willis** received the B.S. degree (*summa cum laude*) in electrical engineering with a minor in computer science from The University of Texas at Dallas (UT Dallas), Richardson, TX, USA, in 2020. At UT Dallas, he engaged in the development of algorithms for real-time human-computer interaction algorithms for mm-wave radar. After graduating in summer 2020, he entered the finance industry as a quantitative analyst.

**Yiorgos Makris** (Senior Member, IEEE) received the Diploma degree in computer engineering from the University of Patras, Patras, Greece, in 1995, and the M.S. and Ph.D. degrees in computer engineering from the University of California at San Diego, San Diego, CA, USA, in 1998 and 2001, respectively.

After spending a decade on the faculty of Yale University, New Haven, CT, USA, he joined The University of Texas at Dallas (UT Dallas), Richardson, TX, USA, where he is currently a Professor

of electrical and computer engineering, leading the Trusted and RELiable Architectures (TRELA) Research Laboratory, and the Safety, Security and Healthcare Thrust of the Texas Analog Center of Excellence (TxACE). His research interests include applications of machine learning and statistical analysis in the development of trusted and reliable integrated circuits and systems, with particular emphasis on the analog/RF domain.

Dr. Makris was a recipient of the 2006 Sheffield Distinguished Teaching Award, the Best Paper Awards from the 2013 IEEE/ACM Design Automation and Test in Europe (DATE 2013) Conference and the 2015 IEEE VLSI Test Symposium (VTS 2015), and the Best Hardware Demonstration Awards from the 2016 and 2018 IEEE Hardware-Oriented Security and Trust Symposia (HOST 2016 and HOST 2018). He has served as an Associate Editor for the IEEE TRANSACTIONS ON INFORMATION FORENSICS AND SECURITY, the IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS, and the IEEE Design and Test of Computers Periodical and as a Guest Editor for the IEEE TRANSACTIONS ON COMPUTERS and SYSTEMS.

**Kenneth K. O** (Fellow, IEEE) received the B.S., M.S., and Ph.D. degrees in electrical engineering and computer science from the Massachusetts Institute of Technology, Cambridge, MA, USA, in 1984, 1984, and 1989, respectively.

From 1989 to 1994, he worked at Analog Devices Inc., developing submicrometer CMOS processes for mixed-signal applications, and high-speed bipolar and BiCMOS processes. He has been a Professor with the University of Florida, Gainesville, FL, USA, from 1994 to 2009. He is currently the Direc-

tor of the Texas Analog Center of Excellence and the TI Distinguished University Chair Professor of analog circuits and systems with The University of Texas at Dallas, Richardson, TX, USA. He has authored or coauthored  $\sim$ 280 journal and conference publications. He holds 15 patents. His research group is developing circuits and components required to implement analog and digital systems operating at frequencies up to 40 THz using silicon IC technologies.

Dr. O. received the 2014 Semiconductor Research Association University Researcher Award. He was the President of the IEEE Solid-State Circuits Society in 2020 and 2021.